Tool/software:

Hi Champ,

I am asking for my customer.

They are testing with giving the same DAC value in mulitiple CMPSS modules for PCM control. The I_sense signal is connected to the positive input of CMPSS.

It turned out a severe current unbalancing in multi-phases topology.

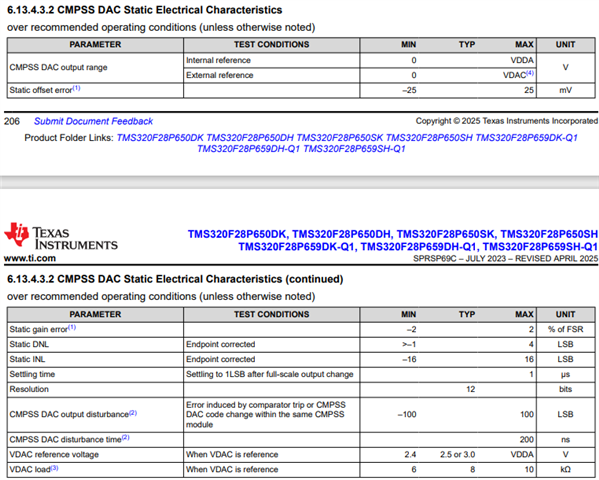

(1). The worst case scenario, the static error of DAC static could be as much as 25mV from offset + 66mV from gain (2% of full scale range), right ? Did I miss any parameter ?

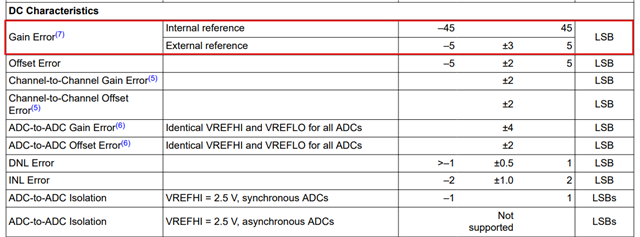

Besides, I should also consider the ADC gain error (45 LSB) for causing multi-phases current unbalancing here, right ?

(2). The static offset error can be compensated/calibrated in the software, right ? could the gain error be compensated/calibrated (2% of full scale range) in any way ?

(3). Since customer will also add ramp generator in next step, there is a CMPSS DAC Dynamic Error.

Is the Max. total CMPSS DAC error be 25mV from offset + 66mV from gain + DYNAMICERROR ? could the DAC Dynamic Error be compensated/calibrated in any way ?

Thanks and regards,

Johnny