Tool/software:

Dear support team,

I have worked with Mcan peripheral, and before approaching the questions I make an introduction.

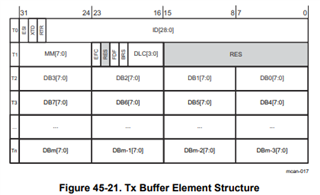

According to document SPRUIZ1B the TX Buffer Element Structure drawn on figure 35-21 page 5216 is for

- classic CAN peripheral : FDF = 0

- FD CAN peripheral : FDF = 1

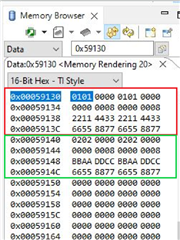

According TI API and TI example "mcan_ex7_classic_transmit.c" , the function MCAN_writeMsgRam is used to fill the C structure MCAN_TxBufElement, whose data field is

uint16_t data[MCAN_MAX_PAYLOAD_BYTES];

#define MCAN_MAX_PAYLOAD_BYTES (64U)

The mentioned structure allocates on "RAM TX buffer", something that in "FD CAN" is called TX buffers and in "classic CAN peripheral" is called TX mailbox.

My consideration about the use of Mcan peripheral as "classic CAN peripheral" and driven by TI API is that: for every TX buffers allocated in RAM, a waste of ( 64 - 8 ) = 56 byte takes place.

Is my consideration correct ?

If yes, is there in TI API a TX BUFFER ELEMENT C structure, that has MAX_PAYLOAD_BYTES equals to 8, and its related C function to allocate it as "standard TX buffer element" ?

I would avoid the mentioned waste and using Mcan peripheral with API functions.

Thank you for your support,

Ettore