Part Number: TMS320F28P650DK

Other Parts Discussed in Thread: LAUNCHXL-F28P65X

Tool/software:

Hi all,

I am studying EtherCAT functionality on the P65x device and have the following questions,

- ESCSS_ACCESS_CTRL register bit-10.

- This bit is configured to allow or not allow memory access through the parallel port, what does this mean and how does it work?

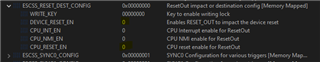

- ESCSS_RESET_DEST_CONFIG register bit-0.

- Is this bit used to enable/disable ESC_PHY_RESETn pin to reset PHY? I ask this question because it seems like ESC_PHY_RESETn pin can reset the PHY, regardless of the setting of this bit.

- ESCSS_CONFIG_LOCK register bit-4.

- This bit is used to allow EtherCAT ports to be connected to the I/O pins. However, regardless of the setting of this bit, the EtherCAT port appears to be connected to the I/O pins.

- The bus width for PDI.

- The Beckhoff ET1100 supports multiple PDIs, and P65x devices support 16-bit ASYNC PDI. Does PDI bus width only affect data access speed? Are there any concerns regarding the PDI bus width (8-bit or 16-bit) ?

Please help me clarify the above questions, thanks for your help.

Luke