Tool/software:

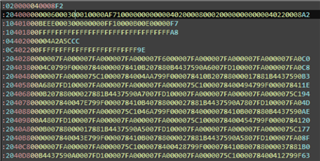

I suspect I have an issue in my linker that is causing address overlap in the resulting Intel Hex file. I have attached linker as reference. I'm having data overlap at address 0x84010 on line 3

CLA_SCRATCHPAD_SIZE = 0x100;

--undef_sym=__cla_scratchpad_end

--undef_sym=__cla_scratchpad_start

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BOOT_RSVD : origin = 0x000002, length = 0x0001AF /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B1, length = 0x00024F

RAMM1 : origin = 0x000400, length = 0x0003F8 /* on-chip RAM block M1 */

RAMD0 : origin = 0x00C000, length = 0x000800

RAMD1 : origin = 0x00C800, length = 0x000800

RAMLS0_3 : origin = 0x008000, length = 0x002000 // RAMLS0, RAMLS0LS1, RAMLS0LS2 and RAMLS3 are combined and used as CLA program memory

RAMLS4_7 : origin = 0x00A000, length = 0x002000 // RAMLS4, RAMLS0LS5, RAMLS0LS6 and RAMLS7 are combined and used as CLA data memory

RAMGS0_1 : origin = 0x00D000, length = 0x002000

RAMGS2_7 : origin = 0x00F000, length = 0x005FFB

RAMGS8 : origin = 0x015000, length = 0x001000

RAMGS9 : origin = 0x016000, length = 0x001000

RAMGS10_11 : origin = 0x017000, length = 0x002000

RAMGS12 : origin = 0x019000, length = 0x001000

RAMGS13 : origin = 0x01A000, length = 0x001000

RAMGS14_15 : origin = 0x01B000, length = 0x001FF8 //RAMGS14, RAMGS15 are combined and used as a ram function for faster execution

FW_FILE_SIZE : origin = 0x014FFB, length = 0x000004

RUN_BL_MARKER : origin = 0x014FFF, length = 0x000001

/* Flash sectors */

GROUP { /* GROUP memory ranges for crc/checksum of entire flash */

BEGIN : origin = 0x084020, length = 0x000002, fill=0xFFFF

FLASH2_13 : origin = 0x084022, length = 0x03BEEE, fill=0xFFFF /* on-chip Flash - FLASH2 to FLASH13 are combined */

NV_DATA : origin = 0x0BFF10, length = 0x0000E0, fill=0xFFFF /* for storing nv data */

} crc(_ccs_flash_checksum, algorithm=CRC16_802_15_4)

CRC_DATA : origin = 0x84000, length = 0x000020, fill=0xFFFF /* for storing auto generated crc */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000800

CMTOCPURAM : origin = 0x038000, length = 0x000800

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

CLA1_MSGRAMLOW : origin = 0x001480, length = 0x000080

CLA1_MSGRAMHIGH : origin = 0x001500, length = 0x000080

CLA1_DMA_MSGRAM : origin = 0x001680, length = 0x000080

DMA_CLA1_MSGRAM : origin = 0x001700, length = 0x000080

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH2_13, ALIGN(8)

.cinit : > FLASH2_13, ALIGN(8)

.switch : > FLASH2_13, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used */

.stack : > RAMM1

.freertosStaticStack: >> RAMGS0_1

.freertosHeap : > RAMGS13

#if defined(__TI_EABI__)

.init_array : > FLASH2_13, ALIGN(8)

.bss : > RAMGS2_7

.bss:output : > RAMGS8

.data : > RAMGS10_11

.sysmem : > RAMGS9

/* Initalized sections go in Flash */

.const : > FLASH2_13, ALIGN(8)

#else

.pinit : > FLASH2_13, ALIGN(8)

.ebss : > RAMGS2_7

.esysmem : > RAMGS9

/* Initalized sections go in Flash */

.econst : >> FLASH2_13, ALIGN(8)

#endif

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

RUN_BL_MARKER_LOCATION : > RUN_BL_MARKER, type=NOINIT

FW_FILE_SIZE_LOCATION : > FW_FILE_SIZE, type=NOINIT

dclfuncs : > FLASH2_13, ALIGN(8)

/* CLA specific sections */

#if defined(__TI_EABI__)

Cla1Prog : LOAD = FLASH2_13,

RUN = RAMLS0_3,

LOAD_START(Cla1funcsLoadStart),

LOAD_END(Cla1funcsLoadEnd),

RUN_START(Cla1funcsRunStart),

LOAD_SIZE(Cla1funcsLoadSize),

ALIGN(8)

#else

Cla1Prog : LOAD = FLASH2_13,

RUN = RAMLS0_3,

LOAD_START(_Cla1funcsLoadStart),

LOAD_END(_Cla1funcsLoadEnd),

RUN_START(_Cla1funcsRunStart),

LOAD_SIZE(_Cla1funcsLoadSize),

ALIGN(8)

#endif

CLADataLS0 : > RAMLS4_7

CLADataLS1 : > RAMLS4_7

Cla1ToCpuMsgRAM : > CLA1_MSGRAMLOW, type=NOINIT

CpuToCla1MsgRAM : > CLA1_MSGRAMHIGH, type=NOINIT

Cla1ToDmaMsgRAM : > CLA1_DMA_MSGRAM, type=NOINIT

DmaToCla1MsgRAM : > DMA_CLA1_MSGRAM, type=NOINIT

Cla1DataRam : > RAMLS4_7

/* CLA C compiler sections */

//

// Must be allocated to memory the CLA has write access to

//

CLAscratch :

{ *.obj(CLAscratch)

. += CLA_SCRATCHPAD_SIZE;

*.obj(CLAscratch_end) } > RAMLS4_7

.scratchpad : > RAMLS4_7

.bss_cla : > RAMLS4_7

cla_shared : > RAMLS4_7

#if defined(__TI_EABI__)

.const_cla : LOAD = FLASH2_13,

RUN = RAMLS0_3,

RUN_START(Cla1ConstRunStart),

LOAD_START(Cla1ConstLoadStart),

LOAD_SIZE(Cla1ConstLoadSize)

#else

.const_cla : LOAD = FLASH2_13,

RUN = RAMLS0_3,

RUN_START(_Cla1ConstRunStart),

LOAD_START(_Cla1ConstLoadStart),

LOAD_SIZE(_Cla1ConstLoadSize)

#endif

NV_DATA_Location : > NV_DATA

.TI.memcrc : > CRC_DATA

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH2_13,

RUN = RAMGS14_15,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

#else

.TI.ramfunc : {} LOAD = FLASH2_13,

RUN = RAMGS14_15,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(8)

#endif

#if defined(__TI_EABI__)

IntProRam : LOAD = FLASH2_13,

RUN = RAMGS9,

LOAD_START(IntProgLoadStart),

LOAD_SIZE(IntProgLoadSize),

LOAD_END(IntProgLoadEnd),

RUN_START(IntProgRunStart),

RUN_SIZE(IntProgRunSize),

RUN_END(IntProgRunEnd),

ALIGN(8)

#else

IntProRam : LOAD = FLASH2_13,

RUN = RAMGS9,

LOAD_START(_IntProgLoadStart),

LOAD_SIZE(_IntProgLoadSize),

LOAD_END(_IntProgLoadEnd),

RUN_START(_IntProgRunStart),

RUN_SIZE(_IntProgRunSize),

RUN_END(_IntProgRunEnd),

ALIGN(8)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

I suspect the following section is causing the overlap, being CRC_AREA the conflicting one. If the linker is placing CRC of the flash group into CRC_DATA, is there a possibility for the application to also write into this section, thus causing the conflict? Since the areas appear to be contiguous, and CRC_DATA is excluded from the group, I'm not 100% certain, so I'm asking for a second eye with more linker experience to point me the possible issue.

GROUP { /* GROUP memory ranges for crc/checksum of entire flash */

BEGIN : origin = 0x084020, length = 0x000002, fill=0xFFFF

FLASH2_13 : origin = 0x084022, length = 0x03BEEE, fill=0xFFFF /* on-chip Flash - FLASH2 to FLASH13 are combined */

NV_DATA : origin = 0x0BFF10, length = 0x0000E0, fill=0xFFFF /* for storing nv data */

} crc(_ccs_flash_checksum, algorithm=CRC16_802_15_4)

CRC_DATA : origin = 0x84000, length = 0x000020, fill=0xFFFF /* for storing auto generated crc */