Tool/software:

I've been trying to utilized the DMA peripheral and encountered some problems.

I can see the addresses are configured accordingly but no data is transferred.

My goal: each ADCA1 event to trigger the DMA copy from the source address to the destination address.

I'm trying to copy 32bit uint32_t data type.

The data copy should be cyclic - once configured I don't want to reconfigure the DMA.

I can also tell the the ADCA1 event functions - I can get into the ISR function which is also triggered from the ADCA1 event.

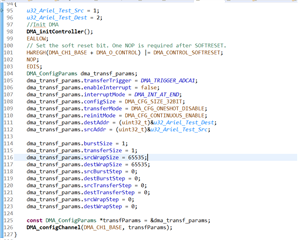

This is my configuration for the DMA:

Is there something I'm missing? Does this configuration matches my needs?

Thanks,

Ariel