Tool/software:

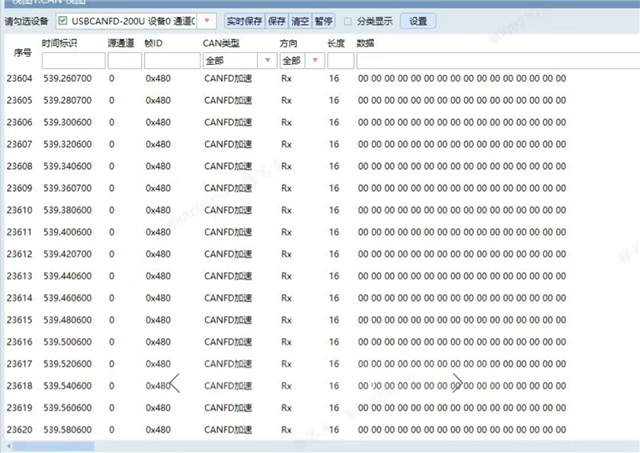

Customer port their firmware from F280039 to F28P55, I confirmed their project has changed all driverlib and header file to F28P55, and now project all function work well on F28P55 except MCAN has issue. The MCAN could send out data with correct ID but content always 0 as below capture. I have attach the customer MCAN code, appreciate expert review if any setting wrong? The MCAN code is totally same as their F280039 project and can work ok in F280039.

/** **********************************************************************

* @copyright ����������ص����ɷ�����˾ ��ͨ��ҵ��

* @file Drv_MCAN.c

* @author HUHAOMING

* @date 2023-03-01

* @version V1.0.0

* @brief �����������ʼ���������ͺ�������

* @remarks ��

**************************************************************************/

#include"F28x_Project.h"

//#include "driverlib.h"

//#include "device.h"

//#include"UDSCAN.h"

//#include "inc/stw_types.h"

//#include "inc/stw_dataTypes.h"

//#define CANDRV_C_TX_PHY_ADDR_STD_CANMSGID 0x780

typedef struct

{

uint8_t MailBox; //�����

uint32_t MsgId; //id

uint32_t MsgIdMask;//����

}CAN_CFG;

typedef struct

{

uint8_t MailBox; //�����

uint32_t MsgId; //id

uint32_t MsgIdMask;//����

uint8_t txMsg_fdf; //CANFDѡ��

uint8_t txMsg_xtd; //��չ֡��֡ѡ��

}CAN_CFG_TX;

uint32_t MCanGetDataLen(uint32_t dlc);

static void MCAN_calcMsgRamParamsStartAddr(MCAN_MsgRAMConfigParams *msgRAMConfigParams);

#define MCAN0_BASE MCANA_MSG_RAM_BASE

//#define MCAN_STD_ID_FILT_START_ADDR (0x0U)

//#define MCAN_STD_ID_FILTER_NUM (6U)

//#define MCAN_EXT_ID_FILT_START_ADDR (0x0U)

//#define MCAN_EXT_ID_FILTER_NUM (2U)

//#define MCAN_TX_BUFF_START_ADDR (0x80U)

//#define MCAN_TX_BUFF_SIZE (10U)

////#define MCAN_FIFO_1_START_ADDR (0xc0U)

////#define MCAN_FIFO_1_NUM (10U)

//#define MCAN_TX_EVENT_START_ADDR (0x100U)

//#define MCAN_TX_EVENT_SIZE (10U)

#define MCAN_EXT_ID_AND_MASK (0x1FFFFFF0U)

//#define MCAN_RX_BUFF_START_ADDR (948U)

//#define MCAN_FIFO_0_START_ADDR (548U)

//#define MCAN_FIFO_0_NUM (5U)

//#define MCAN_FIFO_1_START_ADDR (748U)

//#define MCAN_FIFO_1_NUM (5U)

// Global Variables.

//uint8_t u8TxBuff[64]={1,2,3,4,5,6,7,8};

/* brief Macros to represent the MCAN STD, EXT and TX/RX Elememt Size*/

#define MCAN_MSG_RAM_STD_ELEM_SIZE (1U)

/**< Standard ID Filter Element Size */

#define MCAN_MSG_RAM_EXT_ELEM_SIZE (2U)

/**< Extended ID Filter Element Size */

#define MCAN_MSG_RAM_TX_RX_ELEM_SIZE (18U)

//#define MCAN_STD_ID_FILT_START_ADDR (0x0U)

//#define MCAN_STD_ID_FILTER_NUM 18U//(5U) //RX�������

//#define MCAN_EXT_ID_FILT_START_ADDR (MCAN_STD_ID_FILT_START_ADDR + ((MCAN_STD_ID_FILTER_NUM * 1U * 4U)))//(0x0U)

//#define MCAN_EXT_ID_FILTER_NUM (2U)

//#define MCAN_FIFO_0_START_ADDR (MCAN_EXT_ID_FILT_START_ADDR + ((MCAN_EXT_ID_FILTER_NUM * 2U * 4U)))//(548U)

#define MCAN_FIFO_0_NUM 5//CANRxMailNO

//#define MCAN_FIFO_1_START_ADDR (MCAN_FIFO_0_START_ADDR + (18U * 4U * MCAN_FIFO_0_NUM))//(748U)

#define MCAN_FIFO_1_NUM 24//(0U)

//#define MCAN_TX_EVENT_START_ADDR (MCAN_FIFO_1_START_ADDR + (18U * 4U * MCAN_TX_BUFF_SIZE))//(0x100U)

//#define MCAN_TX_EVENT_SIZE (0U)

//#define MCAN_TX_BUFF_START_ADDR (MCAN_TX_EVENT_START_ADDR + (18U * 4U * MCAN_TX_EVENT_SIZE))//(0x80U)

//#define MCAN_TX_BUFF_SIZE (8U) //TX�������

const CAN_CFG CanRxCfg[CANRxMailNO]=

{//�����;����ID ����

{0, RX_MSGID_1, 0x1ffffff0},

//��֡��0 ��ʼ

{1, CANDRV_C_RX_PHY_ADDR_STD_CANMSGID, 0x7ff},

{2, CANDRV_C_RX_FUNC_ADDR_STD_CANMSGID, 0x7ff},

{3, VCU_0x214, 0x7ff},

{4, VCU_0x481, 0x7ff},

// {5, BMS_0x3A4, 0x7ff},

{5, ESP_0x185, 0x7ff},

{6, TBOX_0x551, 0x7ff},

{7, BMS_0x201, 0x7ff},

// {9, BMS_0x202, 0x7ff},

{8, PDCU_0x236, 0x7ff},

{9, PDCU_0x634, 0x7ff},

{10, VCU_0x64E, 0x7ff},

{11, BMS_0x217, 0x7ff},

{12, VCU_0x484, 0x7ff},

{13, PDCU_0x511, 0x7ff},

{14, VCU_0x631, 0x7ff},

{15, NM_RX_ID, 0x700},

};

const CAN_CFG_TX CanTxCfg[CANTxMailNO]=

{//�����, ����ID, ����, CANFD, ��չ֡

{0, TX_MSG_MEGMEET_ID, 0x1ffffff0, 0, 1 },

{1, CANDRV_C_TX_PHY_ADDR_STD_CANMSGID, 0x7ff, 1, 0 },

{2, OBC_0x518, 0x00, 1, 0 },

{3, OBC_0x521, 0x00, 1, 0 },

{4, OBC_0x480, 0x00, 1, 0 },

{5, OBC_0x666, 0x00, 1, 0 },

{6, OBC_0x6D2, 0x00, 1, 0 },

{7, OBC_0x6D3, 0x00, 1, 0 },

{8, OBC_0x6D4, 0x00, 1, 0 },

{9, OBC_0x6D6, 0x00, 1, 0 },

{10, OBC_0x6D7, 0x00, 1, 0 },

{11, NM_TX_ID, 0x00, 0, 0 },

};

uint32_t MCanGetDataLen(uint32_t dlc)

{

uint32_t dataSize[16] = {0, 1, 2, 3, 4, 5, 6, 7, 8,

12, 16, 20, 24, 32, 48, 64};

if(dlc < 16)

{

return(dataSize[dlc]);

}

else

{

return 0;

}

}

static void MCAN_calcMsgRamParamsStartAddr(MCAN_MsgRAMConfigParams

*msgRAMConfigParams)

{

int32_t status = 0;

uint32_t startAddr = 0U;

/* Compute the start Address and populate the Message RAM configuration

* parameters */

/* 11-bit filter configuration */

/* Assign only if configured */

if (msgRAMConfigParams->lss != 0U)

{

msgRAMConfigParams->flssa = startAddr;

}

/* 29-bit filter configuration */

startAddr += ((msgRAMConfigParams->lss) *

MCAN_MSG_RAM_STD_ELEM_SIZE * 4U);

if (msgRAMConfigParams->lse != 0U)

{

msgRAMConfigParams->flesa = startAddr;

}

/* Tx buffer configuration */

startAddr += ((msgRAMConfigParams->lse) *

MCAN_MSG_RAM_EXT_ELEM_SIZE * 4U);

if ((msgRAMConfigParams->txBufNum != 0U) ||

(msgRAMConfigParams->txFIFOSize != 0U))

{

msgRAMConfigParams->txStartAddr = startAddr;

msgRAMConfigParams->txBufElemSize = MCAN_ELEM_SIZE_64BYTES;

}

/* Tx Event FIFO configuration */

startAddr += ((msgRAMConfigParams->txBufNum) *

MCAN_MSG_RAM_TX_RX_ELEM_SIZE * 4U);

startAddr += ((msgRAMConfigParams->txFIFOSize) *

MCAN_MSG_RAM_TX_RX_ELEM_SIZE * 4U);

if (msgRAMConfigParams->txEventFIFOSize != 0U)

{

msgRAMConfigParams->txEventFIFOStartAddr = startAddr;

}

/* Rx FIFO 0 configuration */

startAddr += ((msgRAMConfigParams->txEventFIFOSize) *

MCAN_MSG_RAM_EXT_ELEM_SIZE * 4U);

if (msgRAMConfigParams->rxFIFO0size != 0U)

{

msgRAMConfigParams->rxFIFO0startAddr = startAddr;

msgRAMConfigParams->rxFIFO0ElemSize = MCAN_ELEM_SIZE_64BYTES;

}

/* Rx FIFO 1 configuration */

startAddr += ((msgRAMConfigParams->rxFIFO0size) *

MCAN_MSG_RAM_TX_RX_ELEM_SIZE * 4U);

if (msgRAMConfigParams->rxFIFO1size != 0U)

{

msgRAMConfigParams->rxFIFO1startAddr = startAddr;

msgRAMConfigParams->rxFIFO1ElemSize = MCAN_ELEM_SIZE_64BYTES;

}

/* Rx Buffer configuration */

startAddr += ((msgRAMConfigParams->rxFIFO1size) *

MCAN_MSG_RAM_TX_RX_ELEM_SIZE * 4U);

msgRAMConfigParams->rxBufStartAddr = startAddr;

msgRAMConfigParams->rxBufElemSize = MCAN_ELEM_SIZE_64BYTES;

}

//#define NUM_OF_MSG (12U)

//#define MCAN_STD_ID_FILTER_NUM (0U)

//#define MCAN_EXT_ID_FILTER_NUM (0U)

//#define MCAN_FIFO_0_NUM (0U)

//#define MCAN_FIFO_0_ELEM_SIZE (MCAN_ELEM_SIZE_64BYTES)

//#define MCAN_FIFO_1_NUM (0U)

//#define MCAN_FIFO_1_ELEM_SIZE (MCAN_ELEM_SIZE_64BYTES)

//#define MCAN_RX_BUFF_NUM (0U)

//#define MCAN_RX_BUFF_ELEM_SIZE (MCAN_ELEM_SIZE_64BYTES)

//#define MCAN_TX_BUFF_SIZE (NUM_OF_MSG)

//#define MCAN_TX_FQ_SIZE (0U)

//#define MCAN_TX_BUFF_ELEM_SIZE (MCAN_ELEM_SIZE_64BYTES)

//#define MCAN_TX_EVENT_SIZE (0U)

//#define MCAN_STD_ID_FILT_START_ADDR (0x0U)

//#define MCAN_EXT_ID_FILT_START_ADDR (MCAN_STD_ID_FILT_START_ADDR + ((MCAN_STD_ID_FILTER_NUM * MCANSS_STD_ID_FILTER_SIZE_WORDS * 4U)))

//#define MCAN_FIFO_0_START_ADDR (MCAN_EXT_ID_FILT_START_ADDR + ((MCAN_EXT_ID_FILTER_NUM * MCANSS_EXT_ID_FILTER_SIZE_WORDS * 4U)))

//#define MCAN_FIFO_1_START_ADDR (MCAN_FIFO_0_START_ADDR + (MCAN_getMsgObjSize(MCAN_FIFO_0_ELEM_SIZE) * 4U * MCAN_FIFO_0_NUM))

//#define MCAN_RX_BUFF_START_ADDR (MCAN_FIFO_1_START_ADDR + (MCAN_getMsgObjSize(MCAN_FIFO_1_ELEM_SIZE) * 4U * MCAN_FIFO_1_NUM))

//#define MCAN_TX_BUFF_START_ADDR (MCAN_RX_BUFF_START_ADDR + (MCAN_getMsgObjSize(MCAN_RX_BUFF_ELEM_SIZE) * 4U * MCAN_RX_BUFF_NUM))

//#define MCAN_TX_EVENT_START_ADDR (MCAN_TX_BUFF_START_ADDR + (MCAN_getMsgObjSize(MCAN_TX_BUFF_ELEM_SIZE) * 4U * (MCAN_TX_BUFF_SIZE + MCAN_TX_FQ_SIZE)))

/*******************************************************************************

** ��������: MCAN_CfgInit

** ��������:��ʼ��can fd

** �䡡 ��: ��

** �䡡 ��: ��

** �����: LINJUNSHENG 2022��09��19��

*******************************************************************************/

void MCAN_CfgInit(void)

{

uint8_t i=0;

MCAN_InitParams initParams;

MCAN_MsgRAMConfigParams msgRAMConfigParams;

MCAN_BitTimingParams bitTimes;

MCAN_StdMsgIDFilterElement stdFiltelem;

MCAN_ConfigParams configParams;

MCAN_ExtMsgIDFilterElement extFiltelem;

//

// Initializing all structs to zero to prevent stray values

//

memset(&initParams, 0, sizeof(initParams));

memset(&msgRAMConfigParams, 0, sizeof(msgRAMConfigParams));

memset(&bitTimes, 0, sizeof(bitTimes));

GPIO_setPinConfig(DEVICE_GPIO_CFG_MCANRXA);

GPIO_setPinConfig(DEVICE_GPIO_CFG_MCANTXA);

SysCtl_setMCANClk(SYSCTL_MCANA, SYSCTL_MCANCLK_DIV_4);

initParams.fdMode = 0x1U; // FD operation enabled.

initParams.brsEnable = 0x1U; // Bit rate switching for

// transmissions enabled.

initParams.txpEnable = 0x0U; // Transmit pause disabled.

initParams.efbi = 0x0U; // Edge filtering disabled.

initParams.pxhddisable = 0x0U; // Protocol exception handling enabled

initParams.darEnable = 0x0U; // Enable Automatic retransmission of

// messages not transmitted successfully

initParams.wkupReqEnable = 0x1U; // Wakeup request is enabled.

initParams.autoWkupEnable = 0x1U; // Auto-Wakeup is enabled.

initParams.emulationEnable = 0x1U; // Emulation/Debug Suspend is enabled.

initParams.tdcEnable = 0x1U; // Transmitter Delay Compensation is

// enabled.

initParams.wdcPreload = 0xFFU; // Start value of the Message RAM

// Watchdog Counter preload.

//

// Transmitter Delay Compensation parameters.

//

initParams.tdcConfig.tdcf = 0xAU;

initParams.tdcConfig.tdco = 0x6U;

//

// Initialize MCAN Config parameters.

//

configParams.monEnable = 0x0U; // Bus Monitoring Mode is disabled

configParams.asmEnable = 0x0U; // Normal CAN operation.

configParams.tsPrescalar = 0xFU; // Prescaler Value.

configParams.tsSelect = 0x2U; // External Timestamp counter value used.

configParams.timeoutSelect = MCAN_TIMEOUT_SELECT_CONT;

// Time-out counter source select.

configParams.timeoutPreload = 0xFFFFU; // Start value of the Timeout

// Counter.

configParams.timeoutCntEnable = 0x0U; // Time-out Counter is disabled.

configParams.filterConfig.anfe = 0x1U; // Accept in Rx FIFO 1.

configParams.filterConfig.anfs = 0x1U; // Accept in Rx FIFO 1.

configParams.filterConfig.rrfe = 0x1U; // Filter remote frames with

// 29-bit extended IDs.

configParams.filterConfig.rrfs = 0x1U; // Filter all remote frames with

// 11-bit standard IDs.

// // Tx Buffer Element Size.

msgRAMConfigParams.lss = MCAN_STD_ID_FILTER_NUM;

msgRAMConfigParams.lse = MCAN_EXT_ID_FILTER_NUM;

msgRAMConfigParams.txBufNum =0;// MCAN_TX_BUFF_SIZE;

// Number of Dedicated Transmit Buffers

msgRAMConfigParams.txFIFOSize = MCAN_TX_BUFF_SIZE;//

msgRAMConfigParams.txBufMode = 0U; //Tx FIFO operation

// Tx Event FIFO Start Address.

msgRAMConfigParams.txEventFIFOSize = 0;//MCAN_TX_BUFF_SIZE;

// Event FIFO Size.

msgRAMConfigParams.txEventFIFOWaterMark = 3U;

// Rx FIFO0 Start Address.

msgRAMConfigParams.rxFIFO0size = MCAN_FIFO_0_NUM;

// Number of Rx FIFO elements.

msgRAMConfigParams.rxFIFO0waterMark = 3U; // Rx FIFO0 Watermark.

msgRAMConfigParams.rxFIFO0OpMode = 0U; // FIFO blocking mode.

// Rx FIFO1 Start Address.

msgRAMConfigParams.rxFIFO1size = MCAN_FIFO_1_NUM;

// Number of Rx FIFO elements.

msgRAMConfigParams.rxFIFO1waterMark = 3U; // Level for Rx FIFO 1

// watermark interrupt.

msgRAMConfigParams.rxFIFO1OpMode = 0U; // FIFO blocking mode.

MCAN_calcMsgRamParamsStartAddr(&msgRAMConfigParams);

//

// Initialize bit timings.

//

bitTimes.nomRatePrescalar = 0xBU; // Nominal Baud Rate Pre-scaler

bitTimes.nomTimeSeg1 = 0x2U; // Nominal Time segment before SP

bitTimes.nomTimeSeg2 = 0x0U; // Nominal Time segment after SP

bitTimes.nomSynchJumpWidth = 0x0U; // Nominal SJW

bitTimes.dataRatePrescalar = 0x1U; // Data Baud Rate Pre-scaler

bitTimes.dataTimeSeg1 = 0xAU; // Data Time segment before SP

bitTimes.dataTimeSeg2 = 0x2U; // Data Time segment after SP

bitTimes.dataSynchJumpWidth = 0x2U; // Data SJW

//

// Wait for memory initialization to happen.

//

while(FALSE == MCAN_isMemInitDone(MCANA_DRIVER_BASE))

{

}

//

// Put MCAN in SW initialization mode.

//

MCAN_setOpMode(MCANA_DRIVER_BASE, MCAN_OPERATION_MODE_SW_INIT);

//

// Wait till MCAN is not initialized.

//

while (MCAN_OPERATION_MODE_SW_INIT != MCAN_getOpMode(MCANA_DRIVER_BASE))

{}

//

// Initialize MCAN module.

//

MCAN_init(MCANA_DRIVER_BASE, &initParams);

//

// Configure Bit timings.

//

MCAN_setBitTime(MCANA_DRIVER_BASE, &bitTimes);

//

// Configure Message RAM Sections

//

MCAN_msgRAMConfig(MCANA_DRIVER_BASE, &msgRAMConfigParams);

for(i=0;i<CANRxMailNO;i++)

{

if(CanRxCfg[i].MsgId>0x7ff)//��չ֡

{

extFiltelem.efid1 = CanRxCfg[i].MsgId; // Standard Filter ID 1.

if(CanRxCfg[i].MsgIdMask)//����

{

extFiltelem.efid2 = CanRxCfg[i].MsgIdMask; // Standard Filter ID 2.

extFiltelem.efec = 0x6U; // Set priority and store in FIFO 0 if filter matches

extFiltelem.eft = 0x2U; // Classic filter: SFID1 = filter, SFID2 = mask

}

else

{

extFiltelem.efid2 = 0;

extFiltelem.efec = 0x7U; //Store into Rx Buffer or as debug message, configuration of SFT[1:0] ignored.

extFiltelem.eft = 0x0U; // Range filter from SFID1 to SFID2

}

MCAN_addExtMsgIDFilter(MCAN0_BASE, CanRxCfg[i].MailBox, &extFiltelem);

}

else if(CanRxCfg[i].MsgId)//��֡

{

stdFiltelem.sfid1 = CanRxCfg[i].MsgId; // Standard Filter ID 1.

if(CanRxCfg[i].MsgIdMask)//����

{

stdFiltelem.sfid2 = CanRxCfg[i].MsgIdMask; // Standard Filter ID 2.

stdFiltelem.sfec = 0x6U; // Set priority and store in FIFO 0 if filter matches

stdFiltelem.sft = 0x2U; // Range filter from SFID1 to SFID2

}

else

{

stdFiltelem.sfid2 = 0;

stdFiltelem.sfec = 0x7U; // Set priority and store in FIFO 0 if filter matches

stdFiltelem.sft = 0x0U; // Range filter from SFID1 to SFID2

}

MCAN_addStdMsgIDFilter(MCAN0_BASE, CanRxCfg[i].MailBox, &stdFiltelem);

}

}

//

// Take MCAN out of the SW initialization mode

//

MCAN_setOpMode(MCANA_DRIVER_BASE, MCAN_OPERATION_MODE_NORMAL);

while (MCAN_OPERATION_MODE_NORMAL != MCAN_getOpMode(MCANA_DRIVER_BASE))

{

}

}

/*******************************************************************************

** ��������: MCAN_vTransmit

** ��������:����CAN����

** �䡡 ��: ���ݻ���

** �䡡 ��:ture �ɹ�

** �����: LINJUNSHENG 2022��09��19��

*******************************************************************************/

uint16_t MCAN_vTransmit(const uint8_t* txdata,uint32_t u32Id,uint8_t u8Len)

{

MCAN_TxBufElement txMsg;

uint16_t i = 0U;

uint16_t txMsg_xtd = 0;

uint16_t txMsg_fdf = 0;

uint16_t MailBox = 0;

for(i = 0;i<CANTxMailNO;i++)

{

if(CanTxCfg[i].MsgId == u32Id)

{

txMsg_xtd = CanTxCfg[i].txMsg_xtd;//

txMsg_fdf = CanTxCfg[i].txMsg_fdf;

MailBox = CanTxCfg[i].MailBox;

break;

}

}

if(txMsg_xtd == 1)//��չ֡

{

txMsg.id = (uint32_t)(u32Id)&0x1fffffff; // Identifier Value.

txMsg.xtd = 1U; // 29-bit standard identifier.

}

else//��֡

{

txMsg.id = ((uint32_t)(u32Id)) << 18U; // Identifier Value.

txMsg.xtd = 0U; // 11-bit standard identifier.

}

if(txMsg_fdf == 1)//can or can_fd�ж�

{

txMsg.fdf = 1U; // Frame transmitted in CAN FD

txMsg.brs = 1U; // CAN FD frames transmitted with bit rate

// switching.

}

else

{

txMsg.fdf = 0U; // Frame transmitted in CAN

txMsg.brs = 0U; // CAN FD frames transmitted with bit rate

}

txMsg.rtr = 0U; // Transmit data frame.

txMsg.esi = 0U; // ESI bit in CAN FD format depends only on error

// passive flag.

if(u8Len <= 8) //���ͳ����ж�LYS

{

txMsg.dlc = u8Len;

}

else

{

switch(u8Len)

{

case 12:

txMsg.dlc = 9;

break;

case 16:

txMsg.dlc = 10;

break;

case 20:

txMsg.dlc = 11;

break;

case 24:

txMsg.dlc = 12;

break;

case 32:

txMsg.dlc = 13;

break;

case 48:

txMsg.dlc = 14;

break;

case 64:

txMsg.dlc = 15;

break;

default:

break;

}

}

txMsg.efc = 1U; // Store Tx events.

txMsg.mm = 0xAAU; // Message Marker.

//

// Data bytes.

//

for(i = 0; i < u8Len; i++)

{

txMsg.data[i] = txdata[i] & 0xFF;

}

MCAN_TxFIFOStatus TxFS;

MCAN_getTxFIFOQueStatus(MCAN0_BASE, &TxFS);

if(TxFS.fifoFull==0)

{

MCAN_writeMsgRam(MCAN0_BASE, MCAN_MEM_TYPE_FIFO, TxFS.putIdx, &txMsg);//

MCAN_txBufAddReq(MCAN0_BASE, TxFS.putIdx);

return 1;

}

else

{

return 0;

}

}

uint32_t Drv_CanGetErrorStatus(void)

{

MCAN_ProtocolStatus CanStatus;

MCAN_getProtocolStatus(MCAN0_BASE, &CanStatus);

return CanStatus.busOffStatus;

}

void MCAN_GetErrorCnt(uint8_t *pRCR,uint8_t *pTCR)

{

MCAN_ErrCntStatus ErrCounter;

MCAN_getErrCounters(MCAN0_BASE, &ErrCounter);

*pRCR = ErrCounter.recErrCnt;

*pTCR = ErrCounter.transErrLogCnt;

}

/*******************************************************************************

** ��������: CAN_FrameSend

** ��������:����CAN����

** �䡡 ��: TxMsg ���ݻ���

** �䡡 ��:ture �ɹ�

** �����: LINJUNSHENG 2022��09��19��

*******************************************************************************/

uint8_t CAN_FrameSend(CANFRAME TxMsg)

{

MCAN_vTransmit(TxMsg.Data,TxMsg.CanId.all,TxMsg.u8Len);

return 1;

}

/*******************************************************************************

** ��������: CAN_ConfirmTx

** ��������:����CANȷ��

** �䡡 ��: ���ݻ���

** �䡡 ��:ture �ɹ�

** �����: LINJUNSHENG 2022��09��19��

*******************************************************************************/

uint16_t CAN_ConfirmTx(uint32 ubObjNr)

{

int16 RET = FALSE;

uint32 NbTransmitStatus;

uint32 Nb;

Nb = MCAN_getTxBufTransmissionStatus(MCAN0_BASE);

NbTransmitStatus = (Nb >> ubObjNr)&0x01UL;

// if(( 1U == NbTransmitStatus) && (1U == ((MailBoxSendRequestSts >> ubObjNr)&0x01UL )))

{

// MailBoxSendRequestSts = 0U;

RET = TRUE;

}

return RET;

}

/*******************************************************************************

** ��������: Drv_CANReceiveQuery

** ��������:����CAN����

** �䡡 ��: ��

** �䡡 ��:��

** �����: LINJUNSHENG 2022��09��19��

*******************************************************************************/

void Drv_CANReceiveQuery(void)

{

uint32 rxMsgID;

uint8_t i=0;

uint16 MailIndex;

MCAN_RxNewDataStatus newData;

MCAN_RxBufElement rxMsg;

//rxMsg1msTickCntr++;

CANFRAME CanRxBuff;

uint16_t u16RxLen=0;

MCAN_RxFIFOStatus RxFS;

// MCAN_getNewDataStatus(MCAN0_BASE, &newData);

//

// for(MailIndex = 0U; MailIndex < CANRxMailNO ;MailIndex++ )

// {

// if( 0UL != (( newData.statusLow >> MailIndex ) & 0x01UL))

// {

// MCAN_readMsgRam(MCAN0_BASE, MCAN_MEM_TYPE_BUF, MailIndex,0, &rxMsg);

// if(rxMsg.xtd==0)

// {

// rxMsgID = (rxMsg.id & 0x1FFFFFFFUL) >> 18;

// }

// else

// {

// rxMsgID = rxMsg.id & 0x1FFFFFFFUL;

// }

// CanRxBuff.CanId.all = rxMsgID;

// u16RxLen = MCanGetDataLen(rxMsg.dlc);

// memcpy(CanRxBuff.Data,rxMsg.data,u16RxLen);

// CanRxBuff.u8Len = u16RxLen;

// sCanRxPutQue(CanRxBuff);

// }

// }

// MCAN_clearNewDataStatus(MCAN0_BASE,&newData);

//���������FIFO0Ҫ��Ӧ�Ķ�ȡMCAN_RX_FIFO_NUM_0

// RxFS.num =MCAN_RX_FIFO_NUM_0;

// MCAN_getRxFIFOStatus(MCAN0_BASE, &RxFS);

// if(RxFS.fillLvl)

// {

// MCAN_readMsgRam(MCAN0_BASE, MCAN_MEM_TYPE_FIFO, RxFS.getIdx,RxFS.num, &rxMsg);

// MCAN_writeRxFIFOAck(MCAN0_BASE, RxFS.num,RxFS.getIdx);//��һ��

// MCAN_getRxFIFOStatus(MCAN0_BASE, &RxFS);

// if(rxMsg.xtd==0)

// {

// rxMsgID = (rxMsg.id & 0x1FFFFFFFUL) >> 18;

// }

// else

// {

// rxMsgID = rxMsg.id & 0x1FFFFFFFUL;

// }

// CanRxBuff.CanId.all = rxMsgID;

// u16RxLen = MCanGetDataLen(rxMsg.dlc);

// memcpy(CanRxBuff.Data,rxMsg.data,u16RxLen);

// CanRxBuff.u8Len = u16RxLen;

// sCanRxPutQue(CanRxBuff);

//

// }

//���������FIF1Ҫ��Ӧ�Ķ�ȡMCAN_RX_FIFO_NUM_1

RxFS.num =MCAN_RX_FIFO_NUM_1;

MCAN_getRxFIFOStatus(MCAN0_BASE, &RxFS);

while(RxFS.fillLvl)

{

MCAN_readMsgRam(MCAN0_BASE, MCAN_MEM_TYPE_FIFO, RxFS.getIdx,RxFS.num, &rxMsg);

RxFS.num =MCAN_RX_FIFO_NUM_1;

MCAN_writeRxFIFOAck(MCAN0_BASE, RxFS.num,RxFS.getIdx);//��һ��

MCAN_getRxFIFOStatus(MCAN0_BASE, &RxFS);

if(rxMsg.xtd==0)

{

rxMsgID = (rxMsg.id & 0x1FFFFFFFUL) >> 18;

}

else

{

rxMsgID = rxMsg.id & 0x1FFFFFFFUL;

}

CanRxBuff.CanId.all = rxMsgID;

u16RxLen = MCanGetDataLen(rxMsg.dlc);

memcpy(CanRxBuff.Data,rxMsg.data,u16RxLen);

CanRxBuff.u8Len = u16RxLen;

sCanRxPutQue(CanRxBuff);

if (s_u16CanRxLength >= CAN_RXBUF_SIZE)

{

break;

}

}

}

void SetCanNormal(void)

{

MCAN_setOpMode(MCAN0_BASE, MCAN_OPERATION_MODE_NORMAL);

while (MCAN_OPERATION_MODE_NORMAL != MCAN_getOpMode(MCAN0_BASE));

}