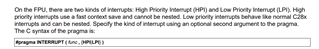

Tool/software:

I have EPWM1A configured to go high on TBCTR=ZERO

With 100MHz SYSCLK and dividers set to /1

I have the ISR configured to trigger at CMPB=10 (for example, I have tried different values). At CMPB=10, I expect the ISR to be triggered at 0.10us plus some interrupt latency.

I am seeing something like 5.37us between the rising edge of EPWM1a and a debug pin that I set in the ISR. I understand there is some interrupt latency between when the interrupt is triggered and when the ISR execution begins, but 5us seems like it may be high.

What type of interrupt latency should I expect on a TBCTR=CMPBU?

A screenshot of the timing and some relevant code snippets are below.

EPWM_setClockPrescaler(epwm_data_ptr->epwm_base, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBaseCounterMode(pc_epwm_ptr->epwm_base, EPWM_COUNTER_MODE_UP);

EPWM_setActionQualifierAction(pc_epwm_ptr->epwm_base,EPWM_AQ_OUTPUT_A,EPWM_AQ_OUTPUT_HIGH,EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(pc_epwm_ptr->epwm_base,EPWM_AQ_OUTPUT_A,EPWM_AQ_OUTPUT_LOW,EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setCounterCompareValue(epwm_data_ptr->epwm_base,EPWM_COUNTER_COMPARE_B, 10);

EPWM_setInterruptSource(epwm_data_ptr->epwm_base, EPWM_INT_TBCTR_U_CMPB);

__interrupt void epwm1_isr(){

GPIO_writePin(124,1);

EPWM_clearEventTriggerInterruptFlag(EPWM1_BASE);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

GPIO_writePin(124,0);

}

I also have deadband enabled, with DBRED=DBFED=40 (Active High Complementary)