Dear TI Experts,

Background:

I am attempting to generate a pulse-skipping scenario by symmetrically enabling and disabling the ePWMA and ePWMB outputs.

ePWM Setup:

-

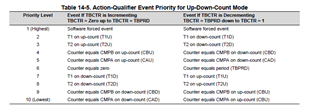

Counter Mode: Up-Down counting

-

TBPRD = 200

-

CMPA = 0 (Based on duty = 100%)

-

CMPA is loaded at Zero Event (

TBCTR == 0) -

Interrupt Source: CMPA match when TBCTR == CMPA while counting down

Query 1 : what happens when TBCTR == CMPA == ZERO (100% duty scenario)?

Assumption: The CMPA match event will be missed in this case, because at TBCTR == 0, the counter is transitioning from down-counting to up-counting. Therefore, the TBCTR == CMPA == ZERO match does not occur while TBCTR is in the down-count phase.

Is this assumption valid?

ePWM Setup:

-

Counter Mode: Up-Down counting

-

TBPRD = 200

-

CMPA = 200 (Based on duty 0%)

-

CMPA is loaded at Zero Event (

TBCTR == 0) -

Interrupt Source: CMPA match when TBCTR == CMPA while counting up

Query 2: What happens when TBCTR == CMPA == TBPRD (0% duty scenario)?

Assumption: The CMPA match event will be missed because at TBCTR == CMPA == TBPRD, the counter reverses direction and starts counting down. Therefore, the TBCTR == CMPA condition does not occur while counting up.

Is this understanding, correct?