Tool/software:

Dear Experts,

I am trying to achieve a simple guard on a PWM signal but it's not clear how to use these modules.

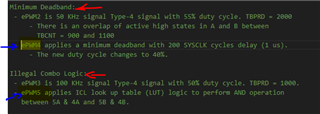

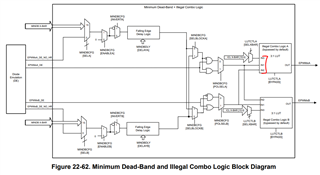

The (one, and very very basic) available example and video appear to mix and combine the minimum deadband and the ICL functionalities.

Is this for a reason ? is there a mandatory link between these two features ? why is there a third EPWM signal entering the table ? do I have to have a signal there even if I'm not using it?

Suppose all I want to achieve is this basic guard:

If EPWM4A and EPWM4B both equal 1, then output 0 to both

Do I have to use the MinDB module in this case? do I have to tie some PWM signal to the lookup table and fill it up with duplicate entries so that it is treated as "X"?

Thank You,

-Alon.