Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Tool/software:

Hi,

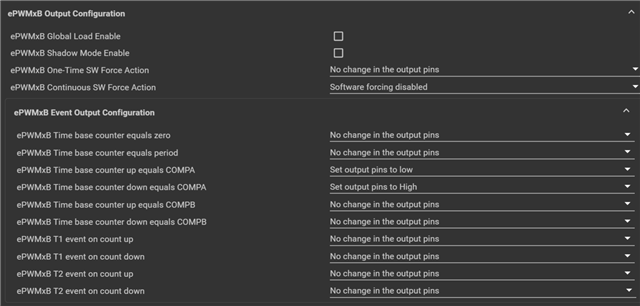

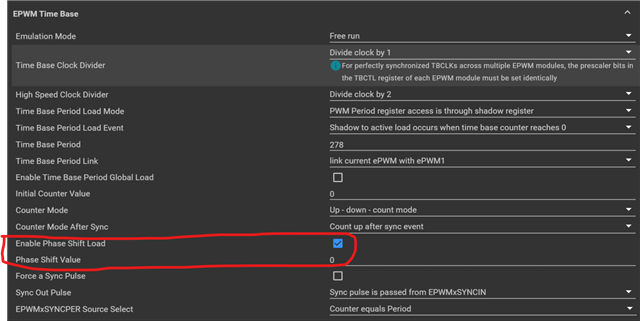

I'm using SysConfig to configure ePWM signals. Configuration for PWMs looks like this:

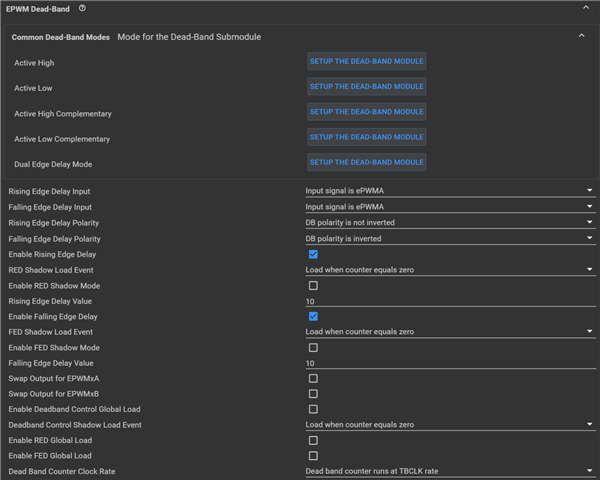

The deadband control is based on active high complimentary presets:

When the enable phase shift load is enabled, even thought the phase shift value is 0, the waveform (PWM1A, PWM1B) will become asymmetric.

The code generated by Sysconfig is

EPWM_enablePhaseShiftLoad(PWM1_BASE);

EPWM_setPhaseShift(PWM1_BASE, 0);

vs

EPWM_disablePhaseShiftLoad(PWM1_BASE);

EPWM_setPhaseShift(PWM1_BASE, 0);

Is this normal/expected? If yes what's the equation for calculating duty cycle of each signal (PWMxA and PWMxB)?

If no, what could be the source of the problem?

Thanks