Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

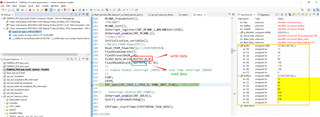

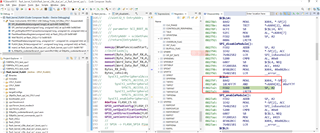

Hello, expert. Currently, I am configuring SPI for the CCS-A project. Since this project does not have sisconfig, I have to configure it myself. Currently, the A project has successfully configured SCI and the sending and receiving are correct, which proves that the low-speed clock of the A project is correct. However, the configuration of SPI is incorrect at present.

I configured SPI correctly in Project B (verified successfully on the development board), but when I transferred the code from Project B to Project A for running, it didn't work properly. Could you please tell me what configuration I'm lacking and how to troubleshoot the issue?

void main(void)

{

//

// flush SCIA TX port by waiting while it is busy, driverlib.

//

// sciaFlush();

//

// initialize device and GPIO, driverlib.

//

Device_init();

Device_initGPIO();

//

// init interrupt and vectorTable, drivelib.

//

Interrupt_initModule();

Interrupt_initVectorTable();

//

//

// Enable Global Interrupt (INTM) and realtime interrupt (DBGM)

//

EINT;

ERTM;

//

// At 200MHz, execution wait-states for external oscillator is 4. Modify the

// wait-states when the system clock frequency is changed.

//

Flash_initModule(FLASH0CTRL_BASE, FLASH0ECC_BASE, 4);

//

// Pump access must be gained by the core using pump semaphore

//

EALLOW;

IPC_claimFlashSemaphore(IPC_FLASHSEM_OWNER_CPU1);

SysCtl_allocateFlashBank(SYSCTL_FLASH_BANK0, SYSCTL_CPUSEL_CPU1);

SysCtl_allocateFlashBank(SYSCTL_FLASH_BANK1, SYSCTL_CPUSEL_CPU1);

SysCtl_allocateFlashBank(SYSCTL_FLASH_BANK2, SYSCTL_CPUSEL_CPU1);

SysCtl_allocateFlashBank(SYSCTL_FLASH_BANK3, SYSCTL_CPUSEL_CPU1);

SysCtl_allocateFlashBank(SYSCTL_FLASH_BANK4, SYSCTL_CPUSEL_CPU1);

//Example_CallFlashAPI();

//

// initialize flash_sectors, fapi + driverlib

//

initFlashSectors();

EDIS;

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SCIA);

SysCtl_setLowSpeedClock(SYSCTL_LSPCLK_PRESCALE_4);

/*SCIA*/

GPIO_setControllerCore(DEVICE_GPIO_PIN_UARTARXDA, GPIO_CORE_CPU1);

GPIO_setPinConfig(DEVICE_GPIO_CFG_UARTARXDA);

GPIO_setDirectionMode(DEVICE_GPIO_PIN_UARTARXDA, GPIO_DIR_MODE_IN);

GPIO_setPadConfig(DEVICE_GPIO_PIN_UARTARXDA, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(DEVICE_GPIO_PIN_UARTARXDA, GPIO_QUAL_ASYNC);

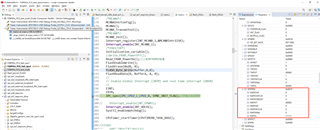

//

// GPIO42 is the SCI Tx pin.

//

GPIO_setControllerCore(DEVICE_GPIO_PIN_UARTATXDA, GPIO_CORE_CPU1);

GPIO_setPinConfig(DEVICE_GPIO_CFG_UARTATXDA);

GPIO_setDirectionMode(DEVICE_GPIO_PIN_UARTATXDA, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(DEVICE_GPIO_PIN_UARTATXDA, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(DEVICE_GPIO_PIN_UARTATXDA, GPIO_QUAL_ASYNC);

SCI_performSoftwareReset(SCIA_BASE);

initSCIA();

Interrupt_register(INT_SCIA_RX, INT_SCIA_BASE_RX_ISR);

Interrupt_register(INT_SCIA_TX, INT_SCIA_BASE_TX_ISR);

SCI_enableTxModule(SCIA_BASE);

SCI_enableRxModule(SCIA_BASE);

Interrupt_enable(INT_SCIA_RX);

Interrupt_enable(INT_SCIA_TX);

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP9);

// //uint32_t EntryAddr;

//

// //

// // parameter SCI_BOOT_ALT5 for GPIO28 (RX),29 (TX)

// //

// //EntryAddr = sciGetFunction(SCI_BOOT_ALT5);

// //return(EntryAddr);

//

memcpy(&RamfuncsLoadStart,&RamfuncsLoadEnd,RamfuncsRunStart);//将初始化Flash代码复制到RAM

//InitFlash();

memset(Byte_Data_Buf_RX,0,sizeof(Byte_Data_Buf_RX));

memset(Byte_Data_Buf_TX,0,sizeof(Byte_Data_Buf_TX));

memset(Word_Data_Buf_RX,0,sizeof(Word_Data_Buf_RX));

memset(Word_Data_Buf_TRX,0,sizeof(Word_Data_Buf_TRX));

Bytes_RX_D=0;

Bytes_cehsi=0;

// SysCtl_setPeripheralAccessControl(SYSCTL_ACCESS_SPIA,

// SYSCTL_ACCESS_CPUX, SYSCTL_ACCESS_FULL);

// SysCtl_setPeripheralAccessControl(SYSCTL_ACCESS_SPIA,

// SYSCTL_ACCESS_CLA1, SYSCTL_ACCESS_FULL);

// SysCtl_setPeripheralAccessControl(SYSCTL_ACCESS_SPIA,

// SYSCTL_ACCESS_DMA1, SYSCTL_ACCESS_FULL);

// SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_SPIA);

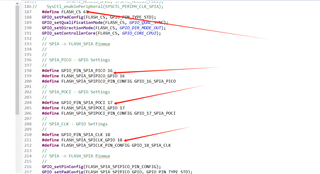

#define FLASH_CS 61

GPIO_setPadConfig(FLASH_CS, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(FLASH_CS, GPIO_QUAL_SYNC);

GPIO_setDirectionMode(FLASH_CS, GPIO_DIR_MODE_OUT);

GPIO_setControllerCore(FLASH_CS, GPIO_CORE_CPU2);

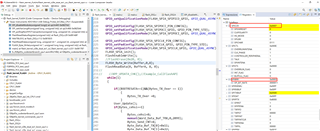

//

// SPIA -> FLASH_SPIA Pinmux

//

//

// SPIA_PICO - GPIO Settings

//

#define GPIO_PIN_SPIA_PICO 16

#define FLASH_SPIA_SPIPICO_GPIO 16

#define FLASH_SPIA_SPIPICO_PIN_CONFIG GPIO_16_SPIA_PICO

//

// SPIA_POCI - GPIO Settings

//

#define GPIO_PIN_SPIA_POCI 17

#define FLASH_SPIA_SPIPOCI_GPIO 17

#define FLASH_SPIA_SPIPOCI_PIN_CONFIG GPIO_17_SPIA_POCI

//

// SPIA_CLK - GPIO Settings

//

#define GPIO_PIN_SPIA_CLK 18

#define FLASH_SPIA_SPICLK_GPIO 18

#define FLASH_SPIA_SPICLK_PIN_CONFIG GPIO_18_SPIA_CLK

//

// SPIA -> FLASH_SPIA Pinmux

//

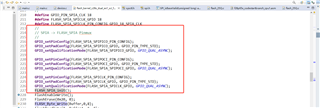

GPIO_setPinConfig(FLASH_SPIA_SPIPICO_PIN_CONFIG);

GPIO_setPadConfig(FLASH_SPIA_SPIPICO_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(FLASH_SPIA_SPIPICO_GPIO, GPIO_QUAL_ASYNC);

GPIO_setPinConfig(FLASH_SPIA_SPIPOCI_PIN_CONFIG);

GPIO_setPadConfig(FLASH_SPIA_SPIPOCI_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(FLASH_SPIA_SPIPOCI_GPIO, GPIO_QUAL_ASYNC);

GPIO_setPinConfig(FLASH_SPIA_SPICLK_PIN_CONFIG);

GPIO_setPadConfig(FLASH_SPIA_SPICLK_GPIO, GPIO_PIN_TYPE_STD);

GPIO_setQualificationMode(FLASH_SPIA_SPICLK_GPIO, GPIO_QUAL_ASYNC);

FLASH_SPIA_init();

FlashEnableWrite();

FlashErase(0x20, 0);

FLASH_Byte_Write(Buffer,0,8);

FlashReadData(0, BufferA, 8, 0);

//

// //APP_UPDATA_CHK();//Example_CallFlashAPI

while(1)

{

}

}

}

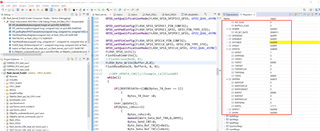

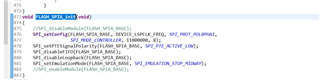

void FLASH_SPIA_init(void)

{

//SPI_disableModule(FLASH_SPIA_BASE);

SPI_setConfig(FLASH_SPIA_BASE, DEVICE_LSPCLK_FREQ, SPI_PROT_POL0PHA1,

SPI_MODE_CONTROLLER, 11000000, 8);

SPI_setPTESignalPolarity(FLASH_SPIA_BASE, SPI_PTE_ACTIVE_LOW);

SPI_disableFIFO(FLASH_SPIA_BASE);

SPI_disableLoopback(FLASH_SPIA_BASE);

SPI_setEmulationMode(FLASH_SPIA_BASE, SPI_EMULATION_STOP_MIDWAY);

//SPI_enableModule(FLASH_SPIA_BASE);

}