Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

Tool/software:

Hello All,

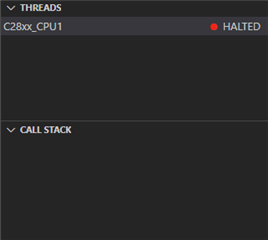

I have a current project I am working on and something that is giving me issues is moving my project from RAM memory to FLASH memory, I have tried excluding the RAM linker file and only including the FLASH linker file. When I do this, the code compiles fine but my problem occurs when I attempt to run the program, this is what I receive:

Searching the technical document, I found the procedure for moving projects from RAM to FLASH:

But I do not see the options for 'Build Configurations' --> 'Set Active' --> 'Flash', only for debug and release and I believe these do not serve the same functionality, I am unsure of whether there is more I need to do in terms of manually changing things around in the linker file itself, in the code, or if I am missing something else. Any help is appreciated!