Part Number: TMS320F28379D

Other Parts Discussed in Thread: C2000WARE

Tool/software:

Hello.

I use the 2 cores on my TMS320F28379D.

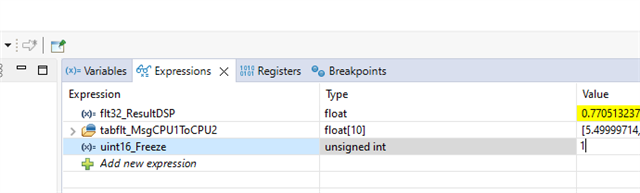

The two cores frequently send messages each other, thanks to the IPC and the MSGRAM.

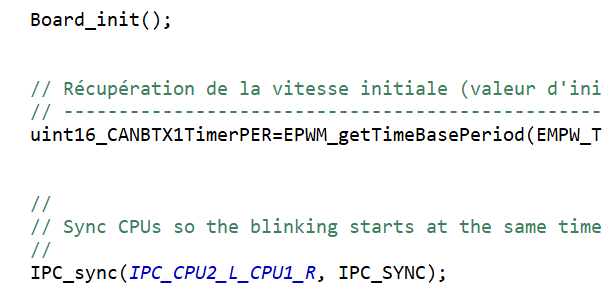

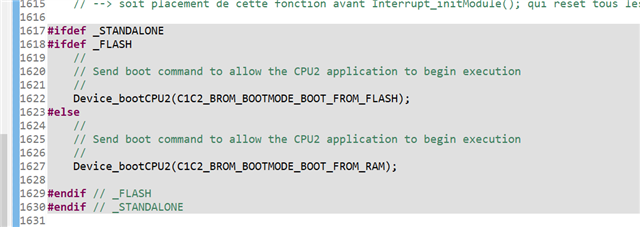

At the begining of CPU1 main function, I put these lines:

So

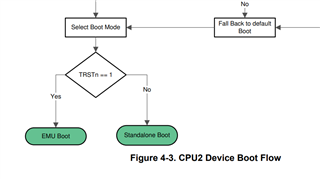

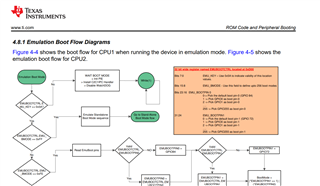

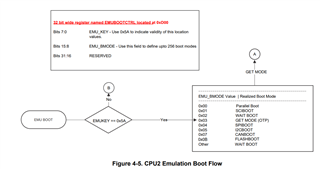

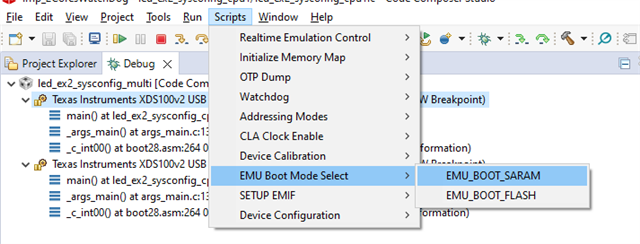

- at the end of the emulation boot, each core jumps at its main() function

- at the end of its standalone boot, the CPU2 receives the adress it has to jump before to go to the main

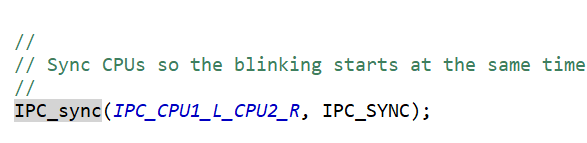

Also I synchronize the 2 cores thanks to IPC_sync():

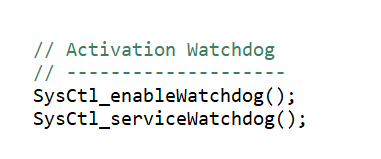

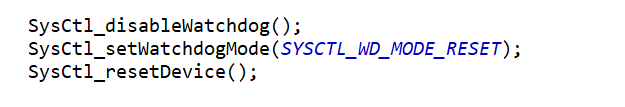

I implemented a watchdog on CPU1, in the interrupt mode. At the end of the ISR, I ask for a reset of the CPU1.

I have many problems and questions.

1) After the reset of CPU1, " the boot ROMs clears all of the system and message RAMs on both CPUs" (TRM)

So I need to reset the CPU2. What is the right way to reset the CPU2 ?

2) Are these resets compliants with the emulation mode ?

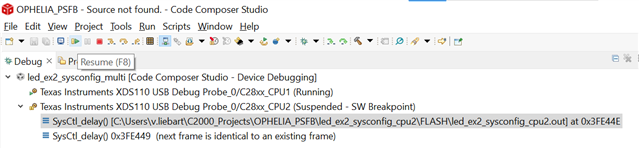

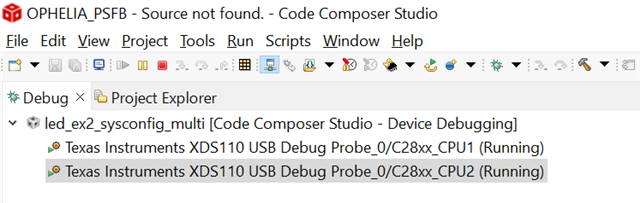

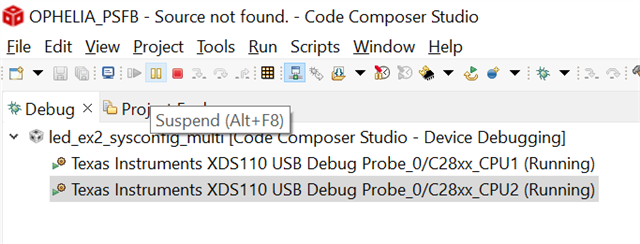

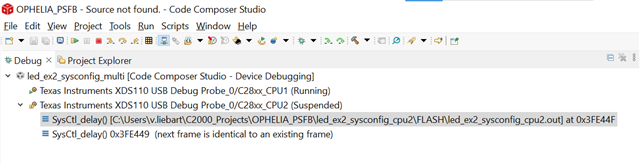

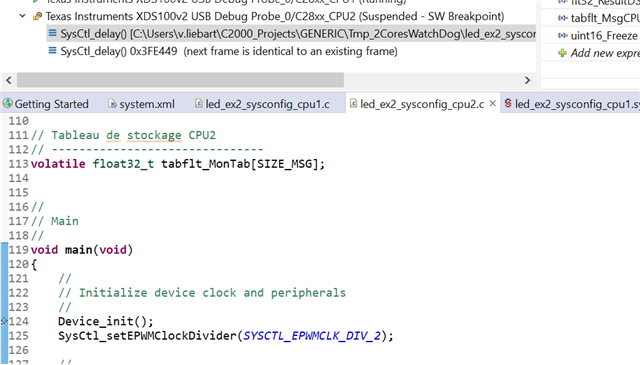

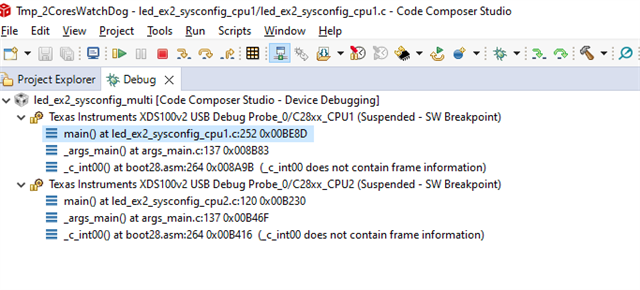

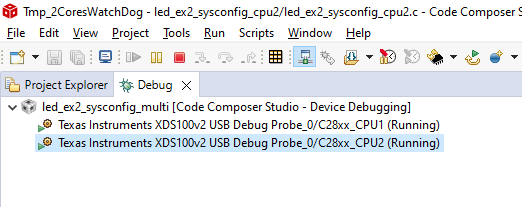

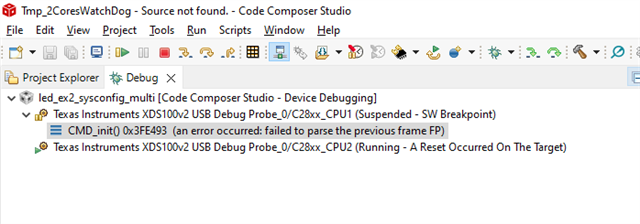

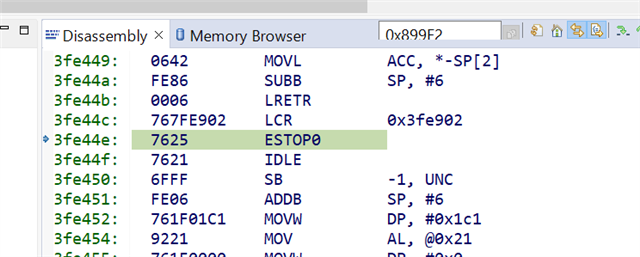

3) When implementing the watchdog on CPU1 only, this behavior surprised me: the CPU1 is reset but the CPU2 seems to be suspended with a BreakPoint I did not implement:

I do not call SysCtl_delay() on my own. Do you have any idea of what happens ? (maybe the solution is to reset CPU2)