Part Number: TMS320F28P650DH

Tool/software:

Hi Experts,

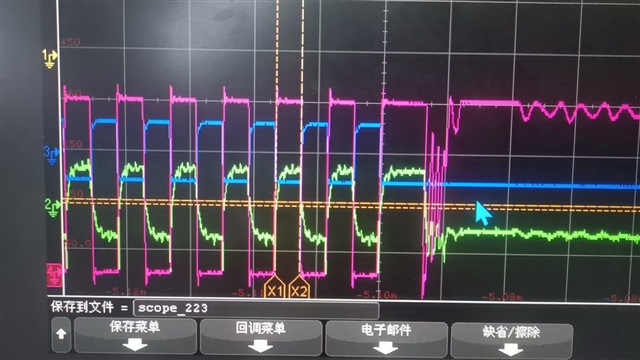

My customer is running power test and they observes strange behavior

It happens sometimes, that most IO would output low for 5 ms, and then restores normal operation.

They tested IO for PWM and several communication peripherals, and they all outputs low when the issue happens.

In the 5 ms duration, the device is not in reset. The ISR still runs normally as they observe the ISR counter. The background loop also runs normally.

It seems that in the 5 ms duration, all IO outputs low and other function of the device is not affected.

This issue only happens with power stages, and it happens some time after power on.

Any idea what might cause this issue?

Regards,

Hang.