Part Number: TMS320F28P650DH

Tool/software:

Hi Experts,

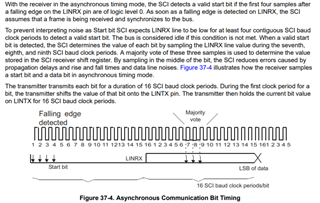

My customer is using LIN as SCI. They find that sometimes the module would miss the first start bit and take the second falling edge as start bit. This would cause an offset in frame read and hence miss the stop bit and issue a frame error.

As the below pictures shows,

The blue is the RX signal. The frame should be read as 0xAB (the lower white box), however, it take the second falling edge as start bit and ends up reading the frame as the upper white box, and issue a frame error.

The yellow is an GPIO indicating frame error, and frame error is the only error issued when this happens.

This only happen sometimes when the power stage is running and there is interference on the RX. As the picture shows, there is a spike before the start bit. They captured multiple error cases and find nearly most causes there is a spike present about 1-bit-time earlier than the fist start bit.

Is there any mechanism that would cause this issue?

This issue is happening of multiple projects that uses F28P65.

Regards,

Hang