Part Number: TMS320F2800157-Q1

Tool/software:

Hi team,

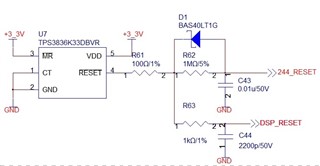

F2800157QPMRQ1 is used as the main control chip, and TPS3836K33DBVR is used as the voltage monitor. I am currently facing a problem that requires assistance in resolving:

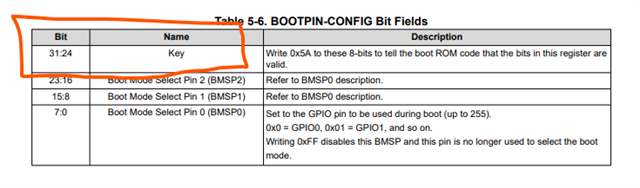

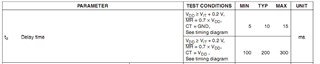

The test found that the SCI mode boot cannot be burned. After powering on, manually lower the reset signal DSP-REET once or pull the reset chip CT signal to 3.3V or 4V before normal burning can be achieved. It is judged that the reset signal is not at a low level for enough time to burn. But the typical value for the reset signal to be at a low level after power on written in the DSP specification is 100us. After actual testing, after connecting four reset chips in series (CT=GND, each chip has a 10ms delay), DSP-REET can burn and boot normally with a 40ms delay relative to VDD.

The following figure shows the specifications of the reset chip regarding output delay (when CT=VDD, the output is delayed by 200ms relative to VDD)

DSP specification sheet explains the delay of reset signal relative to VDD.