Tool/software:

Hi experts,

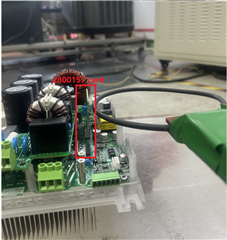

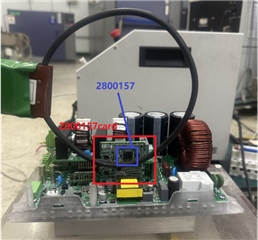

My customer is do wireless EFT on F2800157 as the follow picture:

The pulse generating coil is perpendicular to the card

The pulse generating coil is parallel to the card

The pulse amplitude inside the coil is ±3kV. The pulse generation method complies with IEC61000-4-4.

The distance between the coil and the card changes back and forth between 1cm and 10cm. Customer find that When the coil is 1cm away from the chip, the CPU will freeze and be reset by the watchdog.

For the this EFT is wireless and there is no electrical contact between the coil and the card, I have some question:

1. Do we have a radiation tolerance test report for this chip?

2. For this case, is it necessary to add a metal shield to the chip?

3. Does BU have some suggestions about why the chip will freeze in this test?

PS: Customer feedback that the same test on F28027 is pass. Is the difference in chip manufacturing process between 28027 and 2800157 related to this issue?

Thanks,

Leo