Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi experts,

My customer AIWIN meet the issue that if they trigger SOC continuously, the ADC sampling result will fluctuate on F2800154.

I try to reproduce the issue on 2800157 launchpad based on demo "adc_ex1_soc_software"

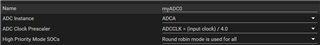

The configuration of ADCA SOC are as follow:

SOC0--A10--sample DACA (the DAC is on another board) output, the DAC output will change between 0.35-3.2V

SOC1--A5--sample DACB (the DAC is on another board) output, the DAC output will fix in 1.65V

SOC2--A0--sample GND

SOC3--A7--sample 3.3V

SOC4--A9--sample GND

The test results are as follows:

1. SOC trigger cycle is 0-1-2-3-4. The result of SOC1 will It will fluctuate between 2000 and 2100

2. I try to change the sample window from 75ns to 750ns and SOC trigger cycle is 0-1-2-3-4. The result of SOC1 will fix at 2048.

3. I try to change the A10 sample source to a fix value and SOC trigger cycle is 0-1-2-3-4. The result of SOC1 will fix at 2048.

4. I try to change the SOC trigger cycle to 0-2-3-4-1. The result of SOC1 will fix at 2000

Why does the sampling change data of one SOC affect the results of another SOC?Is there any other improvement method besides extending the sampling time window?

Thanks,

Leo