Part Number: TMS320F280023

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello

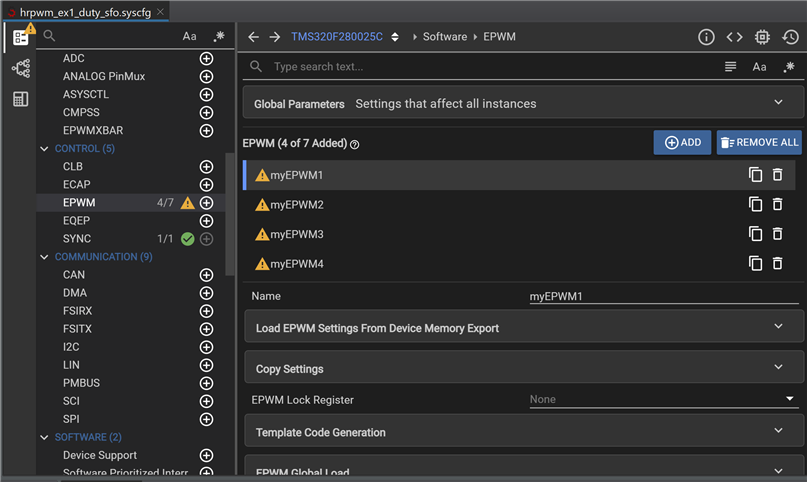

We need to configure the HRPWM of the TMS320F280023 for a flyback converter. We want to avoid any glitch in period or duty cycle while the PWM is running. The frequency can be >1MHz which does not allow any software controlled synchronisation to update period and duty cycle. We concluded, that the only way is to use shadow registers. But it certainly needs some time to update all shadow registers and we want to prevent that there is any transfer to active registers before the software has written a vaild set of data to all shadow registers. For a simultanous and well controlled transfer of all shadow regsiters (period, HR period and duty and HR duty) to active registers we found that the one shot global load should be the right way to do. But there seems to be a problem.

We tried global one shot option to update period, HR period , duty and HR duty simultaneously by writing 1 to GLDCTL2(OSHTLD) only after all shadow registers have been updated by the software. So far it looks like it is working but we discovered the following NOTE: "One-shot load mode must not be used when high-resolution mode is enabled." (SPRUINN7C, page 1790). Now we are confused.

Question 1: Is it still possible to use global load but without one shot instead ( GLDCTL(OSHTMODE=0) )? But this mnode loads active registers continously and we can't delay the shadow to active transfer until all shadow registers are written. How can we disable/enable the shadow to active transfer by software to guarantete that only a valid set of shadow register values are loaded to active registers? If this is not possible: what do you recommend as workaround?

Question 2: Is there any risk of a glich if the shadow registers are beeing updated at exactyl the same time when the hardware is transfering shadow to active? Or with other words: can it happen that a partially written shadow register content is transfered to active registers like period, HR period, duty and HR duty?

We hope for a clear answer that helps to solve our problem. Many thanks in advance for your valuable support.

Best regards

Daniewl Keller