Other Parts Discussed in Thread: SYSCONFIG, C2000WARE, TMS320F280039C

Tool/software:

Hi,

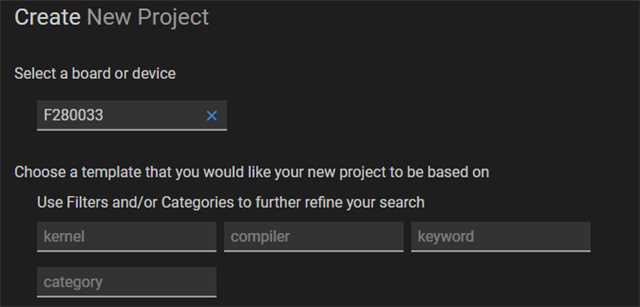

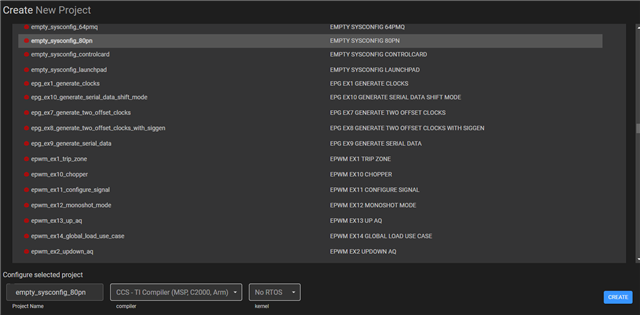

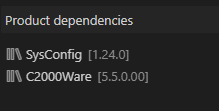

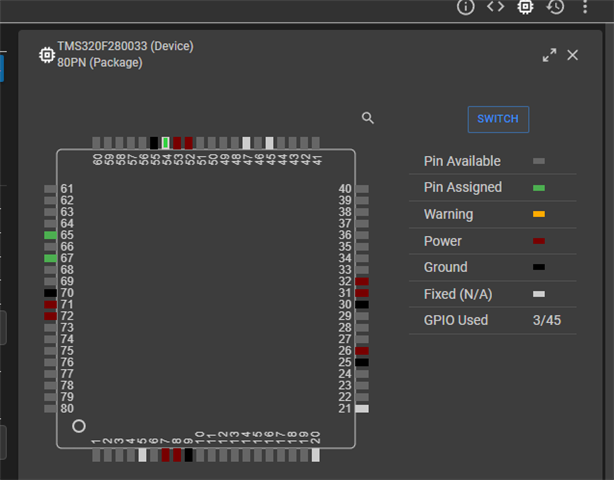

I need to make a test program for one of our projects. I created a new program using the project wizard, with target F280033 and selected example empty_project_80pn, which corresponds to my target. Then I edited the sysconfig file as needed (changed only a few GPIO default state).

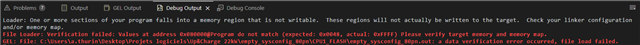

I first programmed with the RAM build, and it worked. But then, I tried to program it with the FLASH build, and got the error :

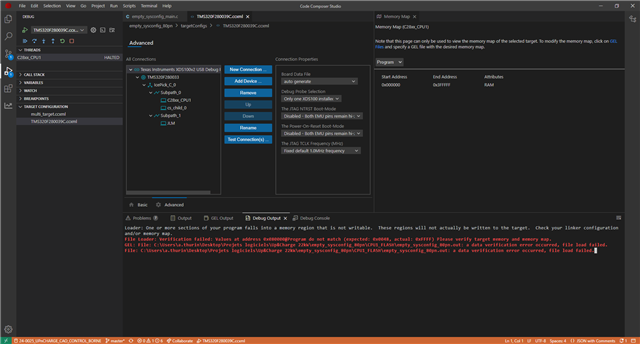

File Loader: Verification failed: Values at address 0x080000@Program do not match (expected: 0x0048, actual: 0xFFFF) Please verify target memory and memory map.

The sysconfig configuration is correct for the target, so is the target configuration file.

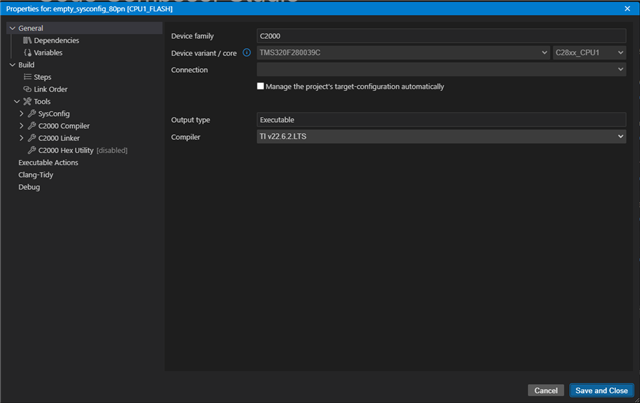

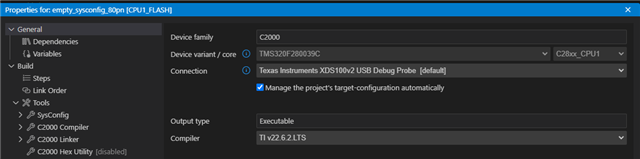

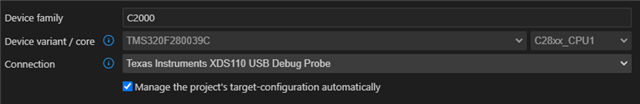

However, when I look at the project properties, I see that the project was configured automatically for the wrong target :

For some reason, I can't change this. I have tried to edit directly the .cproject file, but it reverted to the original setting.

How can I fix this ?

I am a bit worried, because the actual (non-test) code for this project was first developed for the launchpad, and will have to be migrated to an F280033 target too, and I fear I will run into the same issues.

Thanks in advance for your help,

Best regards,

Adrien