Other Parts Discussed in Thread: TMS320F280049C, SYSCONFIG

Tool/software:

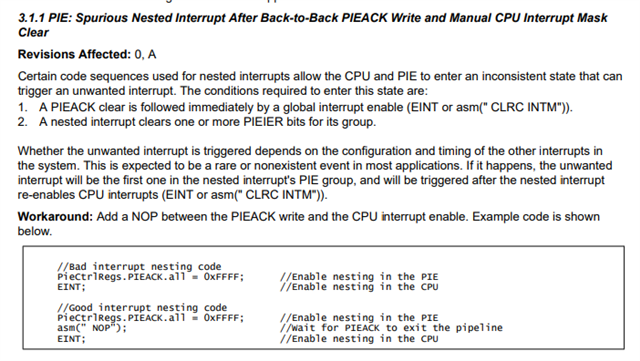

I am having a spurious PIE group 8 interrupt on the TMS320F28P550SG. When running under JTAG debug, the PIE Interrupt vector 88 is being triggered and caught by the default ISR handler. This is interrupt 8.1, which is the I2CA interrupt. However, the issue is that I2C is not used, nor is LIN or SCI-C which are the other peripherals in PIE group 8. Note that when not running under debug, it stalls presumably getting caught in the default ISR handler.

I have read these registers in the unhandled interrupt to understand what is triggering the interrupt

1. PIEIER8 is all-zero

2. PIEIFR8 is all-zero

3. IER.INT8 is zero

4. IFR.INT8 is zero

5. IFR.INT9 is zero

These indicate that there should not be any interrupt being triggered, so I dont understand what is causing this.

I have confirmed that the correct SCI register base address is used in both my code and the generate syscfg code

The code changes that were added leading up to this issue:

- Adding SCI-A setup to syscfg

- Adding code that uses SCI-A

- Adding FreeRTOS task notifications for ISR-to-task and task-to-task sempahore signalling.

The issue appears when the ISR-to-task notification is called. Presumably, the global enable/disable of interrupts allows whatever is happening to propagate.

What are the recommended steps to understand this type off issue?

I should note that I am porting code from the TMS320F280049C, using the same SCI and interrupt handling. From what I can tell, the SCI functionality/API is the same between these two processors.