Part Number: TMS320F280034

Other Parts Discussed in Thread: SYSBIOS, UNIFLASH

Tool/software:

Hi TI Forum,

I'm working with the TMS320F280034 chip and have an issue regarding GPIO internal pull - ups.

1. Reference to Datasheet

In the datasheet (Figure 1: 5.5 Pins With Internal Pullup and Pulldown), it's stated that the pull - ups on GPIO pins are disabled by default after reset. Specifically, for GPIOx, the internal pull - up should be disabled at reset.

2. Observed Behavior in Debug

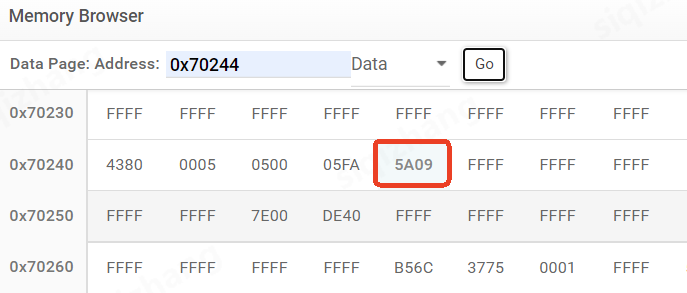

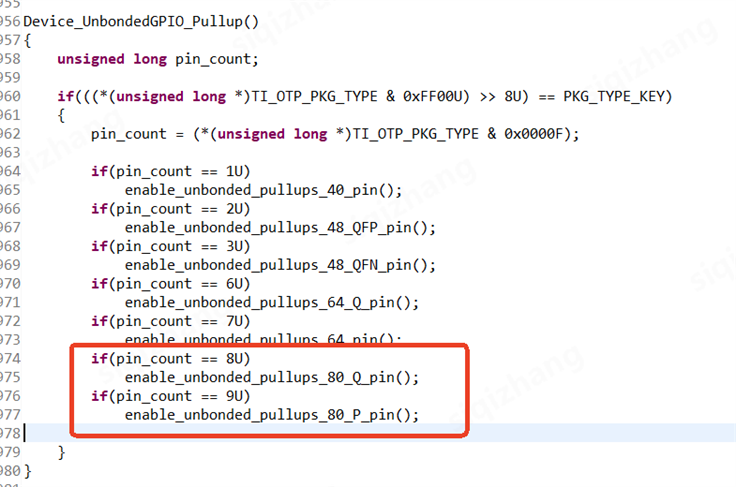

However, when I did an online simulation, before the program ran (Figure 2: Debug view in Code Composer Studio), the GPBPUD register was not all 1s. This caused several IO ports to output a high level. Only when my program initialized the IO pins did the GPBPUD register change to the state where the pull - ups are disabled (values corresponding to pull - up disable).

3. Questions

- Why is the GPBPUD register not in the expected all - 1s state (pull - ups disabled) before the program initializes the IO? Is there something about the boot process or default register values that I'm missing?

- How can I ensure that the GPIO pull - up state is as described in the datasheet (disabled) right after reset, without waiting for the program's IO initialization?

Attached are the relevant figures:

- Figure 1: Datasheet excerpt showing GPIOx pull - up should be disabled at reset.

- Figure 2: Debug view showing GPBPUD register state before program - level IO initialization.

Thanks for your help!

Best regards,

Elena