Tool/software:

Hi experts,

Our customer has encountered the following issues and has some questions:

-

MCAN and IPC Conflict:

When IPC is enabled, MCAN initialization fails. Does TI provide any examples that support both MCAN and IPC functionalities? -

Multi-Core Data Sharing:

Since the customer needs to use MCAN, they are not using IPC functionality. For multi-core data sharing, are there any precautions they should take? In TI’s example, the following code is mentioned:void writeDataCPU1(void)

{

uint16_t index;

//

// Use first location to write a multiplier.

//

cpu1RWArray[0] = multiplier;

for(index = 1; index < 256; index++)

{

cpu1RWArray[index] = index;

//

// The following code will attempt to write to a shared RAM assigned

// to CPU2 and as a result will cause an access violation.

//

// cpu1RArray[index] = 1000 + index;

}

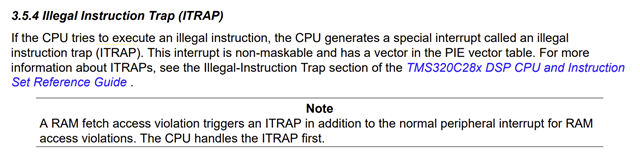

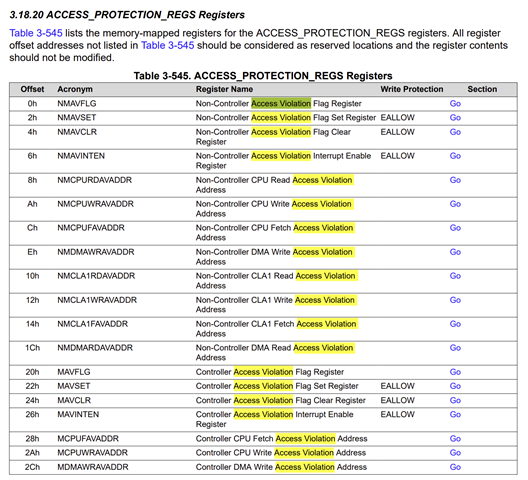

}The example mentions an "access violation." Will this cause the CPU or CLA to generate an exception (fault or trap) that could disrupt normal system operation?

-

Current Multi-Core Data Sharing Approach:

The customer’s current approach is to designate the direction of read/write operations between cores, where the data contributor writes and the data receiver reads. Aside from the issue of data not being refreshed in real-time, are there any other potential risks with this approach?