Part Number: TMS320F2800132

Other Parts Discussed in Thread: TMS320F2800137, C2000WARE

Tool/software:

Dear Sir

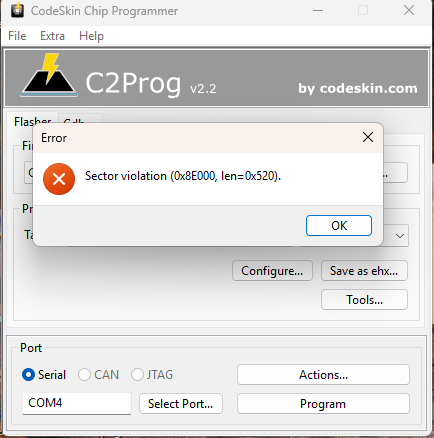

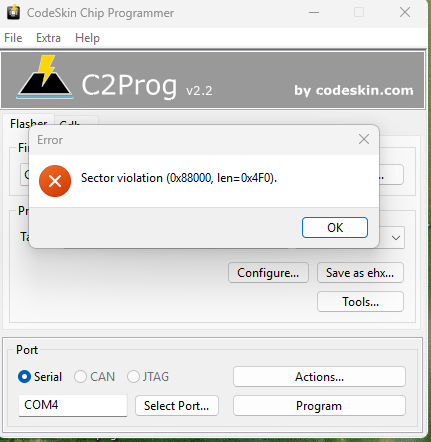

I have taken the example program of Launch pad TMS320F2800137 & changed its target to TMS320F2800132 & build it and then SCI bootloading by C2prog application But i a getting Sector violation error

Please help

With Regards

Yusuf