Tool/software:

Hi,

We are using a TMS320F2838x device on the MCU063B ControlCard. We need to sample 4 independent signals at 1Msps each using 4 ADCs, with the requirement that each ADC samples at the same time (simultaneous sampling). To ensure that the signals are sampled at the same time I use the same PWM (EPWM1) to drive all 4 ADCs. After the EPWM1, there's an ADC SOC, ADC and DMA for each channel. In other words, 4 ADCs, for ADCINT1s and 4 DMA channels and 4 ADC buffers.

EPWM1 (same for all ADCs) -> ADCx SOC0 -> ADCx samples then generates ADCINT1 at the end of conversion -> DMAx is triggered by ADCINT1 from ADCx -> Data buffer x in GS ram for samples

The DMA channels for each ADC are configured to transfer the samples to the data buffers and trigger an interrupt at the end of the transfer. I wait until all DMA channels have completed the transfer of N samples, by configuring each DMA channel to set a different flag. Once all the DMA channels have completed their transfers I display the data and/or send it to a computer for analysis.

Note: I do all the peripheral configuration first and then start the EPWM1 clock last to start triggering the ADCs using the same EPWM1 clock hoping that this method will ensure all the ADCs are sampled simultaneously.

Problem:

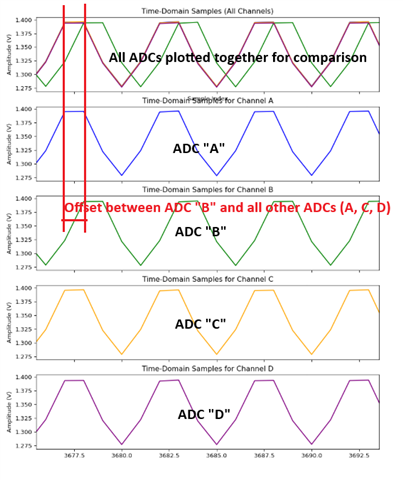

I collected samples using the configuration above and I can see that 1 ADC has a random sample delay compared to the other 3 ADCs. In other words, 3 ADCs are perfectly aligned and 1 ADC is offset by +1, -1 or 0 samples. When I use debug mode, ADC-A (the first ADC to be configured) is almost always the ADC that is offset compared to the other 3 ADCs.

When I flash the program to flash and run from flash, often ADC B (the 2nd ADC to be configured) will be offset compared to the other ADCs.

The delay compared to other channels appears to be random but always (+1, 0, -1) samples.