Part Number: TMS320F28379D

Hello,

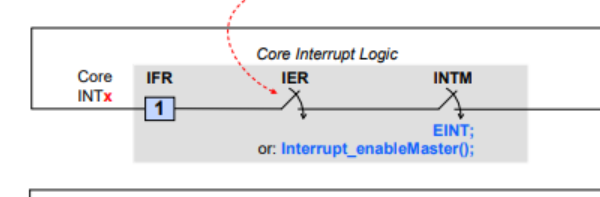

I am familiair with interrupts on this device. But I did not ever dare to set or clear the INTM bit while my application is running.... my question is simple: is there any risk to miss an interrupt signal when using DINT and EINT, or are all the pending interrupts lached, thanks to a pulse generator between IER and INTM on this scheme:

(I mean, since we did not entered into the interrupt, IER is not clear and we will enter in the interrupt as soon as granted)