Part Number: TMS320F28P550SJ

Hi experts,

I found some descripiton mismatch in f28p55 TRM

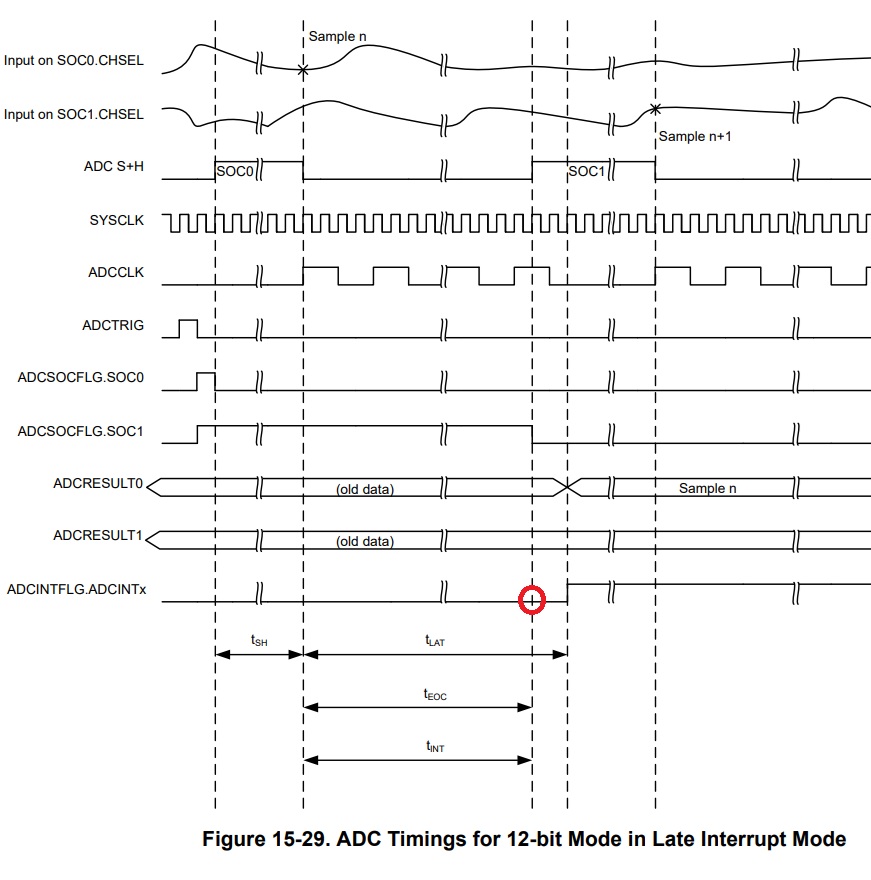

In INTPULSEPOS bit, it describes that Interrupt pulse generation occurs at the end of the conversion, 1 cycle prior to the ADC result latching into its result register.

Q1: Should The interrupt signal be triggerred on the red circle?

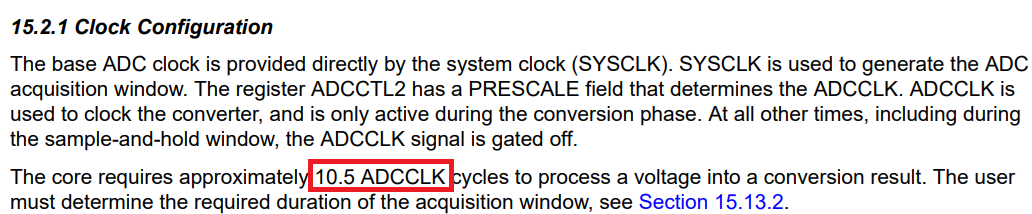

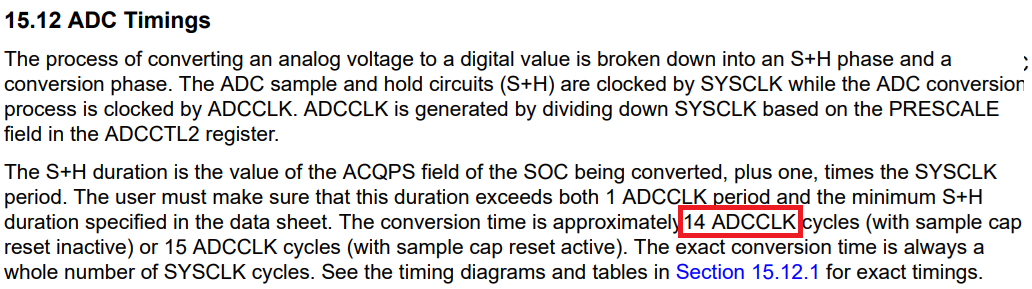

Q2: Which conversion time estimation is correct?

Thanks,

Leo