Part Number: TMS320C5535

Hi All,

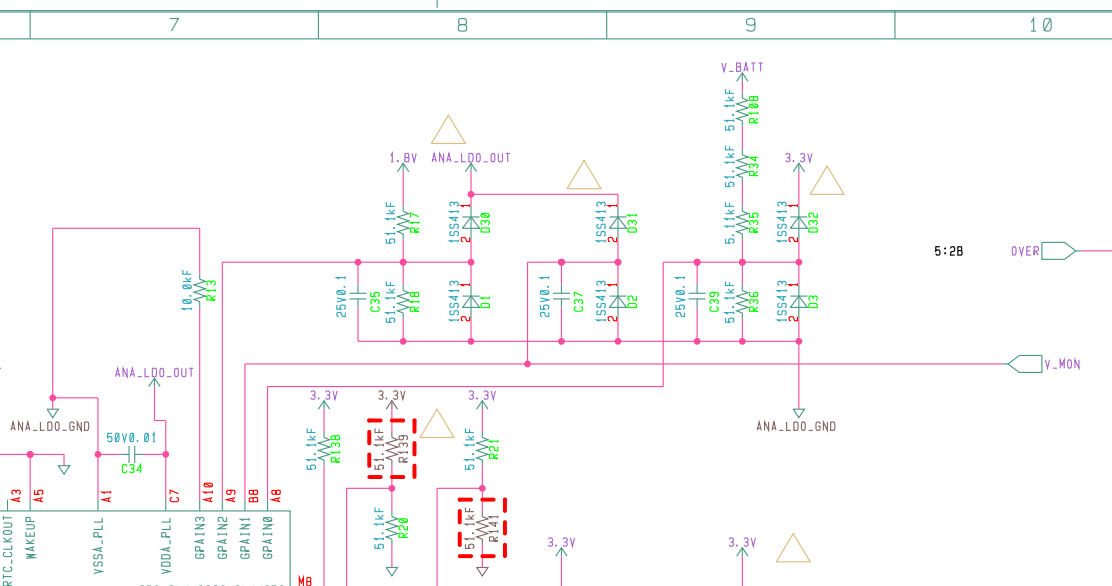

We are using pins GPAIN0–2 to monitor voltages such as 1.8V and the product’s battery level (4V–7V).

However, sometimes the battery level is displayed correctly, and sometimes it is not.

When checking the AD values from the DSP, we see cases where there is an offset of about 10 counts even though there is no input, and cases where there is both an offset and variation in the readings (also about 0–10 counts).

We are currently investigating the cause of this phenomenon.

Initially, we suspected a mounting defect, but X-ray inspection confirmed that there are no issues with the assembly.

Below is the schematic of the relevant section.

Do you see any mistakes in this circuit?

Also, have you encountered similar issues in the past?

If you have any suggestions on methods to investigate the root cause, please let us know.

Best Regards,

Ito