Other Parts Discussed in Thread: TIDA-01606

Hello TI,

Looking for help regarding what the Soft Start ePWM's should look like for TIDA-01606 Reference Design. (3 Level T-Type Inverter / PFC Design; 3 phase 400Vrms to 800Vdc)

The following section describes using RED (Rising Edge Delay) and FED (Falling Edge Delay) to soft start the converter.

Was hoping there were some ePWM waveforms that could be shared for reference.

Using a F28379D ControlCard the following was produced on our end to try and emulate the soft start waveforms.

Conditions:

Environment = Matlab / Simulink

Using Sinusoidal Modulation comparing with ePWM tbprd in up-down mode.

Simulink ePWM Block from C2000 F28379D library.

Emulating PH_A:

ePWM-1 used for HS and AC Mid-Point FETs

ePWM-2 used for LS and DC Mid-Point FETs

Using Deadband set up via ePWM Block Parameters

ACH mode for both ePWM blocks

Deadband period source is set to input port (using a down counter to feed RED and FED ports)

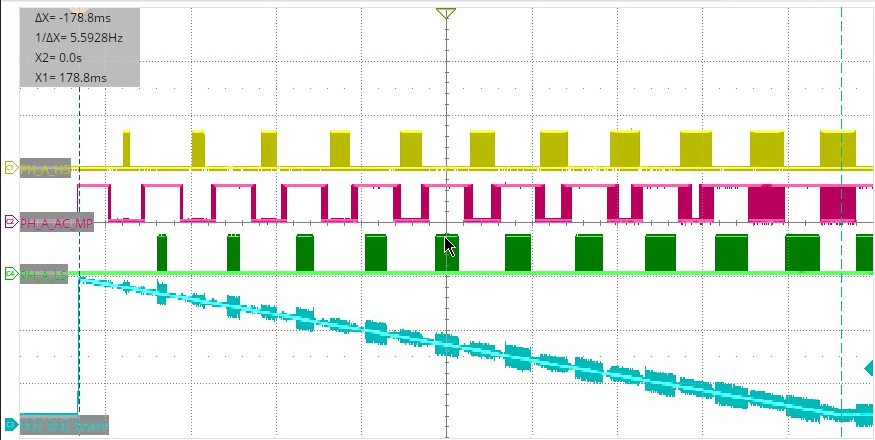

Below is Plot 1 basically using down ramp connected to RED and FED ports on ePWM block.

Scope limited to 4 channels:

Yellow Trace = HS Gate Signal; PH_A

Magenta Trace = AC MP Gate Signal; PH_A

Green Trace = LS Gate Signal; PH_A

Light Blue = RED_FED Dwn Counter ramp (count starts around 1800 stops at desired value of 12)

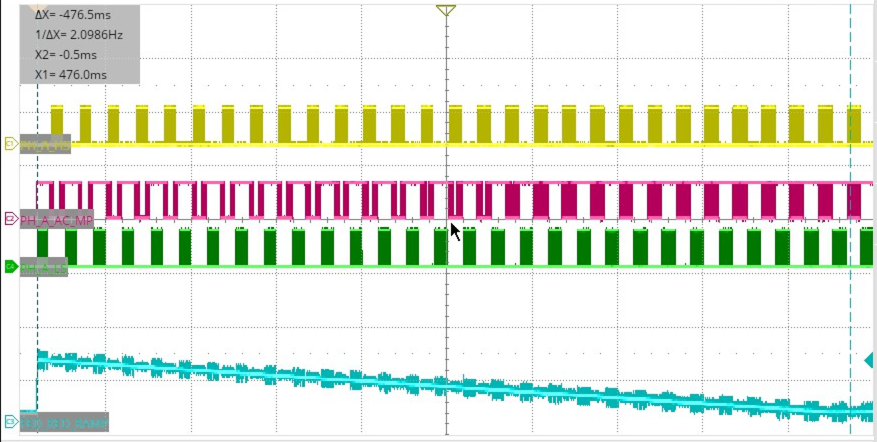

Below is similar Plot but using a different RED_FED Start value, approx 700. Same stop value of 12.

Using a much higher delay in down counter to stretch out the pwms

Comments and Questions:

- Do these ePWMs represent what is being inferred in the TIDA-01606 for Soft Start?

- a. Would this interpretation seem valid if all 3 phases were soft started this same way?

- All ePWMs are using the same Deadband RED FED down ramp signal with;

- AHC

- Using ePWMA for RED FED

- Reload for DBRED and DBFED is "immediate without shadow."

- All ePWMs are using the same Deadband RED FED down ramp signal with;

- a. Would this interpretation seem valid if all 3 phases were soft started this same way?

- If this interpretation is not correct looking help would be appreciated.

Best,

Colin