Dear Team,

The customer is asking CLK frequency of PERIx. LSPCLK in boot sequence.

Could you provide What CLK value set for PERIx. LSPCLK?

External CLK input is 20MHz.

Thanks and Regards,

Hara

Dear Team,

The customer is asking CLK frequency of PERIx. LSPCLK in boot sequence.

Could you provide What CLK value set for PERIx. LSPCLK?

External CLK input is 20MHz.

Thanks and Regards,

Hara

Hi Hara,

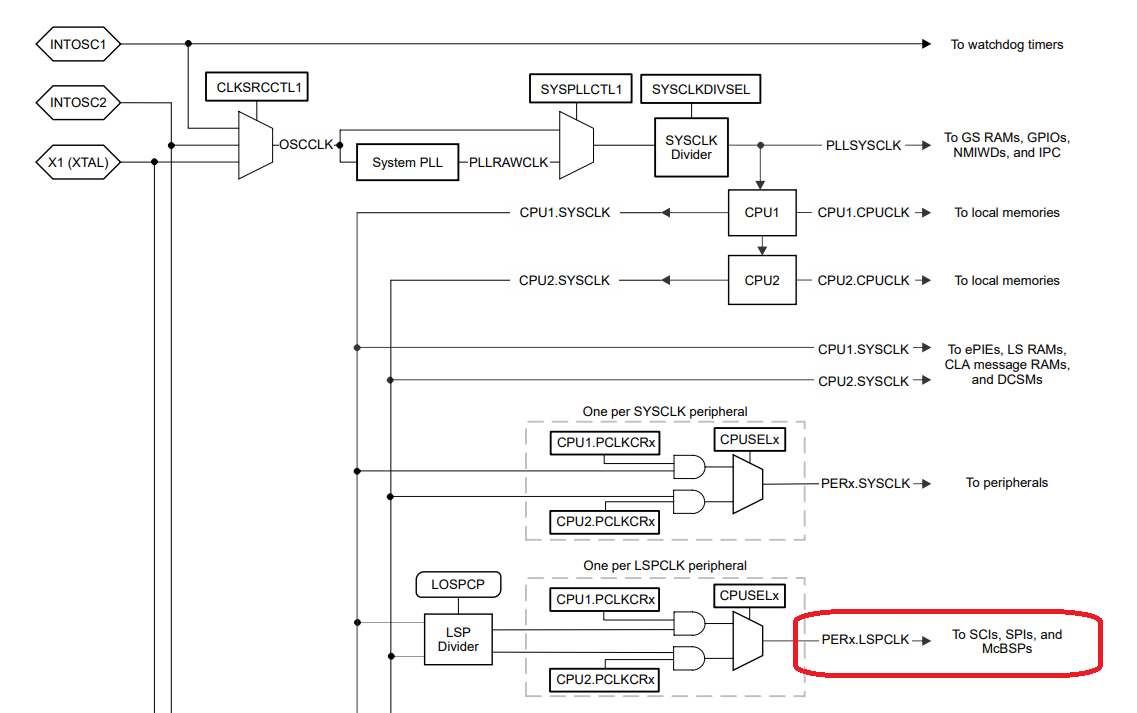

During boot, the PLL is not used, only INTOSC2. In SCI/SPI boot, the LOSPCP is set to /4, more details in Chapter 4.

The default LOSPCP (Low Speed Clock Source Prescalar) is set to /2 aka SYSCLK / 2. At POR, SYSCLKDIVSEL is /1 which would mean your LSPCLK is at 5 MHz by default (unless you're in SCI/SPI boot).

Best Regards,

Aishwarya

Dear Aishwarya,

The below is additional question. Could you also check these please?

Q1. At SCI boot sequence, Are these correct understanding?

INTOSC2:10MHz

LSPCLK:2.5MHz (LOSPCP /4 at SCI boot sequence)

Q2. CLK tree at SCI boot sequence

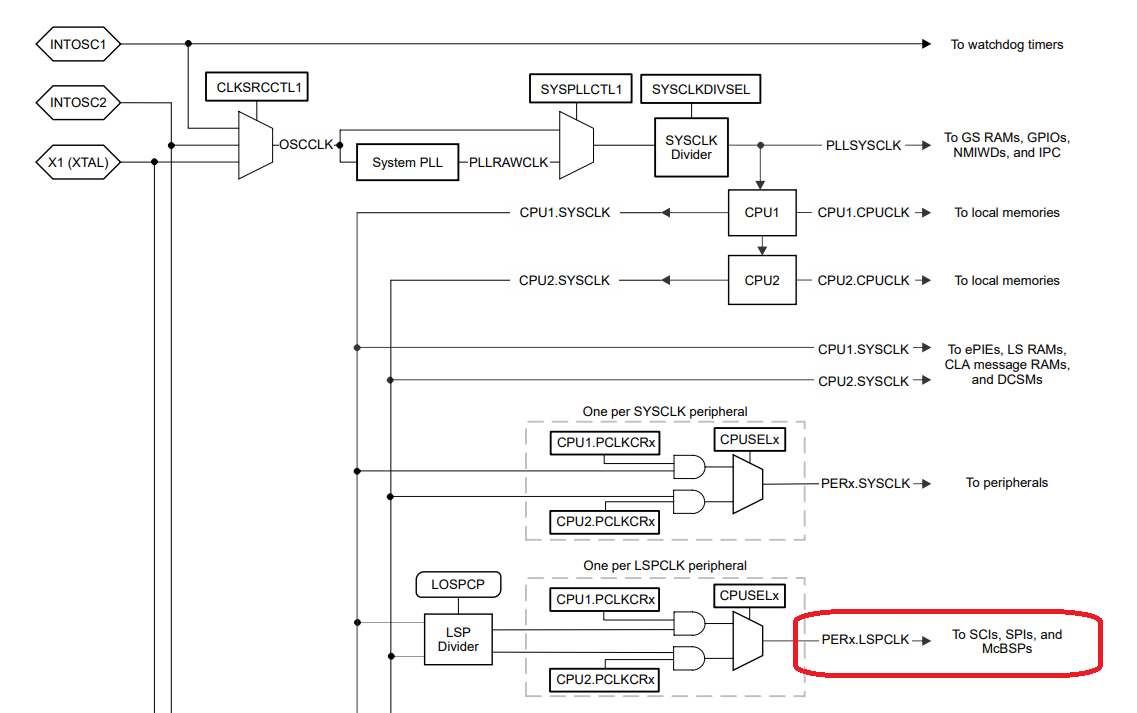

According to the 4.8 note, only INTOSC is used instead of PLL.

There is a route to pass the PLL in the figure below, but there is a concern that the sysclk Divider will be followed by the initial value of SYSCLKDIVSEL /4.

Does it recognize that the sysclk Divider passes at SCI boot sequence?

Q3. Baud rate setting with Auto Baud Detection, Is this correct understanding?

SCI Asynchronous Baud = LSPCLK / ((BRR + 1) *8)

*based on 19.15.2.3 SCIHBAUD Register (Offset = 2h) [Reset = 0000h

Thanks and Regards,

Hara

Hara,

For #1, that's correct.

For #2, SYSCLKDIVSEL is always applied whether or not the PLL is bypassed. As explained earlier and shown in the boot sequence image, the clock dividers config occurs after device resets. Table 4.9.1 Reset Causes and Handling details Boot ROM actions for each reset. In the case of POR, XRSn, etc., the SYSCLKDIVSEL is /1 not /4. This applies for all boot modes.

For #3, that's correct but remember that SCI clock != SCI Baud Rate.

Best Regards,

Aishwarya