Part Number: TMS320F28388D

Issue description:

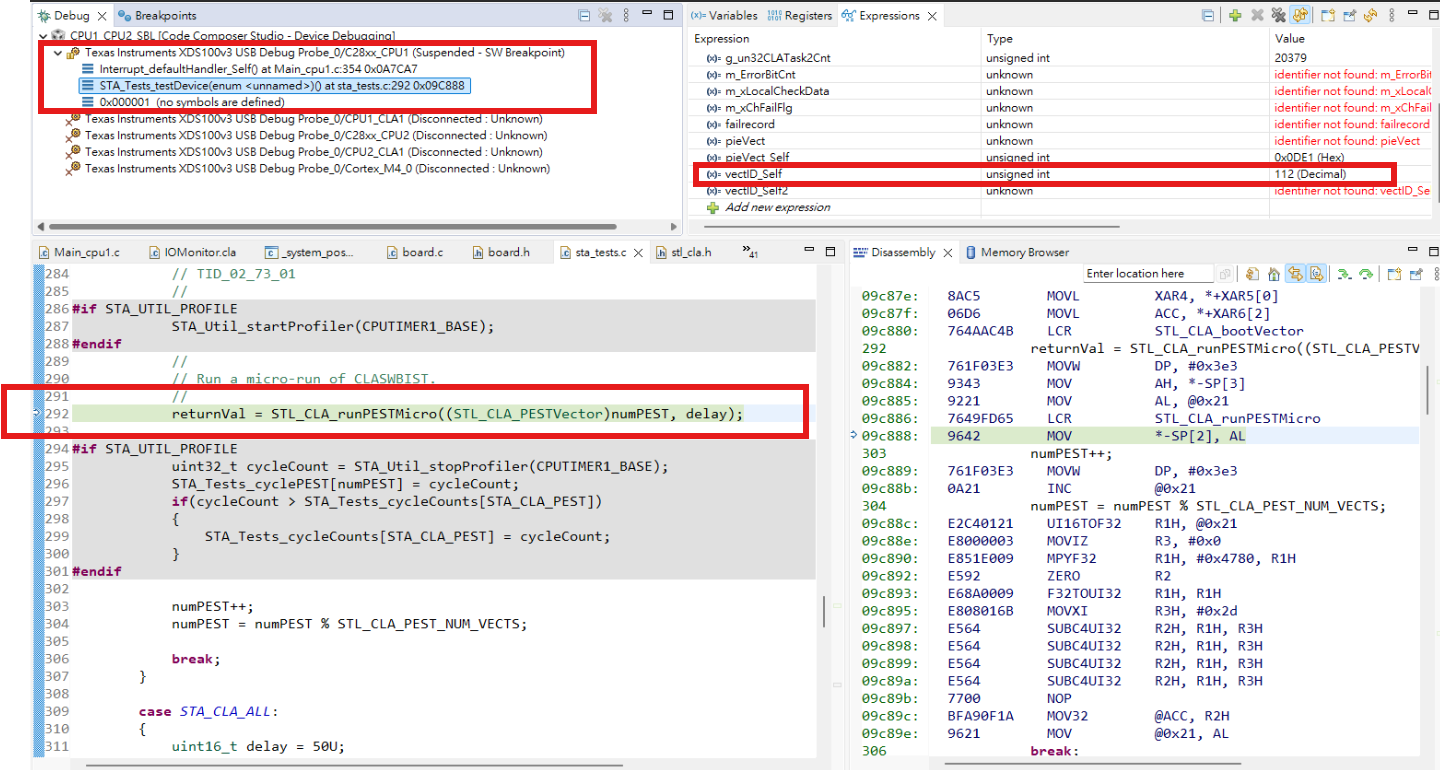

When executing the CLA STL runtime PEST (STL_CLA_runPESTMicro) on F2838x, an unexpected CLA1-related PIE interrupt is occasionally false triggered. The interrupt vector corresponds to PIE Group 11 / INT1 (CLA1_1 interrupt) , even though the interrupt is not intentionally enabled by the application().

In my application, I didn't use the CLA1_Task1 and didn't enable CLA1_1 interrupt, and I checked the PIEIER11 and PIEIFR11 when false triggering happens, the INTx1 are both zeros.

Then I found that once the false triggering happened, the STL_CLA_runPESTMicro() would keep returning STL_CLA_FAIL_TIMEOUT.

Question:

-

Is it expected that CLA STL PEST may assert or route internal signals that can trigger CLA1_1 interrupts and how do I fix this.