Hi folks

We encountered a problem with the C2812's CAN peripheral.

After happily receiving telegrams for more than an hour, suddenly the interrupt stops being called.

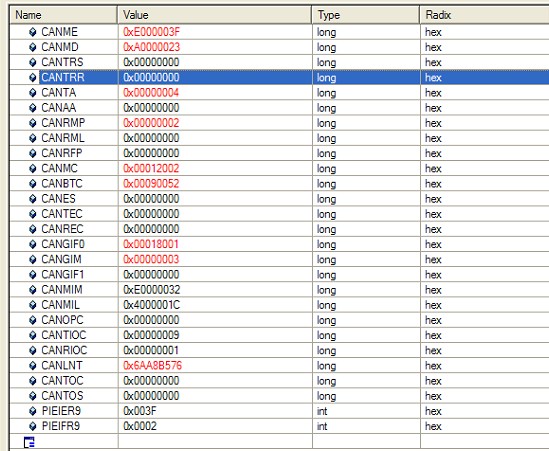

When I debug the controller, I can see that CANRMP has 0x00000002 in it, and CANGIF0.15 is also set. But the interrupt is not called.

When I then acknowledge the RMP by writing 0x02 to it with the emulator, the interrupt starts to work again as soon as the next telegram arrives.

It seems that after the processing of incoming telegrams in the ISR, another one arrives before the ISR is left. And if not all telegrams are handled and the ISR is left, the interrupt never seems to be called again. But how can I assure that no telegram arrives in the time between the processing of the telegrams and the end of the ISR?

I seem to misunderstand something - but what?

Any help is really appreciated!

Regards, Daniel