I am using the SPI port on a TMS320F2812 in a single-master,

multiple slave configuration, and thus must select my

devices with GPIO pins. Devices are serviced asynchronously,

so it is important to know that the prior SPI transaction

has finished before starting a new one. As far as I can

tell, there is no bit in any status register dedicated to

this condition.

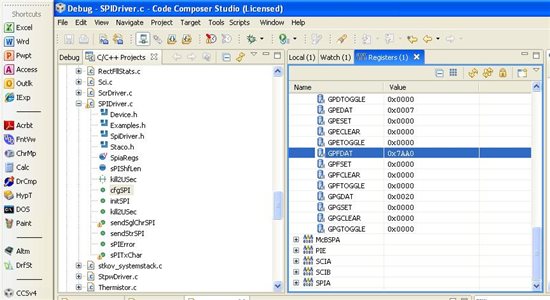

I have had this problem on other processors and got around

it by polling the SPI interrupt bit (SPIST.6 = SPI INT

FLAG). This is giving me trouble as the hardware apparently

sets the bit on the leading edge of the last bit, or half a

bit time before the transaction is complete, causing me to

pull chip select high too soon (sending 0xAA):

SCK ___|¯|_|¯|_|¯|_|¯|_|¯|_|¯|_|¯|_|¯|___

MOSI ___|¯¯¯|___|¯¯¯|___|¯¯¯|___|¯¯¯|_____

1 0 1 0 1 0 1 0

__ __ _____

CS |____________________________|

I got it to work by inserting a 'twiddle-thumbs' loop to

waste 1 bit time after SPI INT FLAG goes true before raising

CS-L, but I don't like kludges.

The SPI reference guide shows the SPISTEA output of the

F2812 staying low all the way to the last clock edge when

operating as a master, and I have confirmed this with my

scope. It occurs to me I could route this signal back in

through an unused GPIO pin and poll it, but again, this

seems like a lot of effort to achieve basic functionality.

Am I missing something obvious?