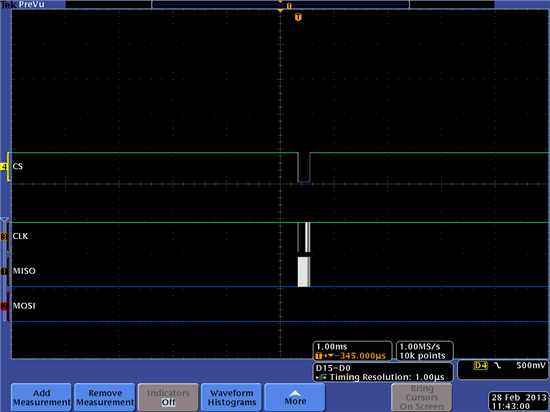

Hi guys I am using the F28335 and I am using the SPI to communicate with a M25P40-VMN6P (4 Mbit, Low Voltage, Serial Flash Memory With 40MHz SPI Bus Interface). I am getting a weird issue that i can't seem to figure out. For some reason the MISO line is riding high when it should be riding low. This is a read command that i am sending to the flash to read whats in the memory. When the line is high it returns all FF.

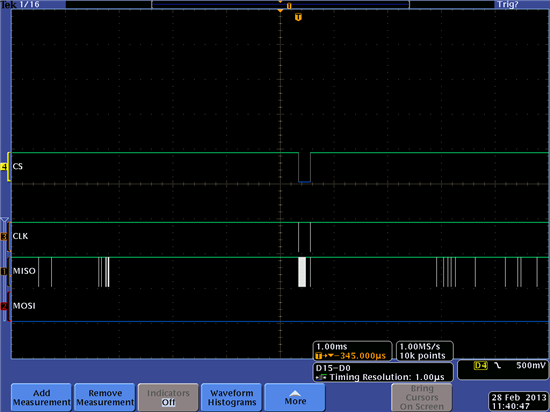

But after I call a second write command followed by a second read command the SPI line drops to low and I am able to read the correct information.

Here is the code i use to initialize the GPIO ports:

GpioCtrlRegs.GPBPUD.bit.GPIO54 = 0; // Enable pull-up on GPIO54 (SPISIMOA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO54 = 3; // Asynch input GPIO54 (SPISIMOA)

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 1; // Configure GPIO54 as SPISIMOA

GpioCtrlRegs.GPBDIR.bit.GPIO54 = 1; //set FRAM CS as out

GpioCtrlRegs.GPBPUD.bit.GPIO55 = 0; // Enable pull-up on GPIO55 (SPISOMIA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO55 = 3; // Asynch input GPIO55 (SPISOMIA)

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 1; // Configure GPIO55 as SPISOMIA

GpioCtrlRegs.GPBPUD.bit.GPIO56 = 0; // Enable pull-up on GPIO56 (SPICLKA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO56 = 3; // Asynch input GPIO56 (SPICLKA)

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 1; // Configure GPIO56 as SPICLKA

GpioCtrlRegs.GPBDIR.bit.GPIO56 = 1; //set FRAM CS as out

GpioDataRegs.GPBSET.bit.GPIO57 = 1; //pre-set FRAM CS high

GpioCtrlRegs.GPBDIR.bit.GPIO57 = 1; //set FRAM CS as out

GpioDataRegs.GPBSET.bit.GPIO58 = 1; //pre-set EEP CS high

GpioCtrlRegs.GPBDIR.bit.GPIO58 = 1; //set EEP CS as out

Here is what is used for a write command to memory:

// SPI_Write:

//---------------------------------------------------------------------------

// This function executes a write, mode 1, on the SPI

//

void SPI_Write(Uint16 CS, Uint16 WA[4],Uint16 WA_count,Uint16 *dp,Uint16 data_length){

//---------------------------------------------------------------------------

// #ifdef RELEASE

Uint16 bs;

Uint16 j;

Uint16 i=0;

// char tempp[1];//trying to find out what CS is

// tempp[0]=CS;//trying to find out what CS is

// if(CS != 0x57 & CS !=0x58){

// SciaTx(tempp);//trying to find out what CS is

if(CS != 57 & CS !=58 & CS!=19 & CS!=15 & CS!=23 ){

SciaTx(String_err);

SciaTx(": Invalid CS");

return;

}

Msg_Flags.bit.Timeout = 0;

CS_Low(CS);

Msg_Flags.bit.spia_rx_rdy = 0;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

SpiaRegs.SPIDAT = SPI_WREN<<8;

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

CS_High(CS); //latch WREN

DELAY_US(1);

CS_Low(CS); //start data tx

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

SpiaRegs.SPIDAT = SPI_WRITE<<8;

Msg_Flags.bit.spia_rx_rdy = 0;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

// SpiaRegs.SPICCR.bit.SPICHAR = 0xF; //set to 16 bit mode

for(j=0;j<WA_count;j++){

SpiaRegs.SPITXBUF = WA[j]<<8;

Msg_Flags.bit.spia_rx_rdy = 0;

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

}

// SpiaRegs.SPICCR.bit.SPICHAR = 0x7; //set to 8 bit mode

while(i<data_length)

{

if(SpiaRegs.SPISTS.bit.BUFFULL_FLAG !=1){

bs = *dp++;

SpiaRegs.SPITXBUF = bs<<8;

i++;

}

}

if(data_length < 2)

{

Msg_Flags.bit.spia_rx_rdy = 0;

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

}

else

{

for(i=0;i<2;i++){ //wait for the last 2 data to be sent

Msg_Flags.bit.spia_rx_rdy = 0;

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

}

}

CS_High(CS); //raise CS for write done

SciaTxByte(data_length);

DELAY_US(5000L); //Time for EEP write

CS_Low(CS); //lower for write disable

SpiaRegs.SPIDAT = SPI_WRDI<<8;

Msg_Flags.bit.spia_rx_rdy = 0;

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

bs = SpiaRegs.SPIRXBUF; //dummy read to clear int

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

CS_High(CS); //raise to latch write disable

//#endif

}

This is the command used to read whats in the buffer:

// SPI_Read:

//---------------------------------------------------------------------------

// This function executes a read, mode 1, on the SPI

//

void SPI_Read(Uint16 CS,Uint16 RA[4],Uint16 RA_count,Uint16 BN){

//---------------------------------------------------------------------------

// #ifdef RELEASE

Uint16 i=0;

Uint16 j;

Uint16 n;

Msg_Flags.bit.Timeout = 0;

if(CS != 57 & CS !=58 & CS!=19 & CS!=15 & CS!=23 ){

// if(CS != 0x57 & CS !=0x58){

SciaTx(String_err);

SciaTx(": Invalid CS");

return;

}

CS_Low(CS); //drop CS to start

Msg_Flags.bit.spia_rx_rdy = 0; //clear flag and interrupt

n = SpiaRegs.SPIRXBUF; //dummy read to clear int

SpiaRegs.SPIDAT = SPI_READ<<8; //send read command

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

// SpiaRegs.SPICCR.bit.SPICHAR = 0xF; //set to 16 bit mode

for(j=0;j<RA_count;j++){

Msg_Flags.bit.spia_rx_rdy = 0; //clear flag and interrupt

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

n = SpiaRegs.SPIRXBUF; //dummy read to clear int

SpiaRegs.SPITXBUF = RA[j]<<8; //send read address

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

}

// SpiaRegs.SPICCR.bit.SPICHAR = 0x7; //set to 8 bit mode

while(i<BN){

Msg_Flags.bit.spia_rx_rdy = 0; //clear flag and interrupt

SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1;

n = SpiaRegs.SPIRXBUF; //dummy read to clear int

SpiaRegs.SPIDAT = 0x00; //dummy write

while(Msg_Flags.bit.spia_rx_rdy != 1){

CpuTimer0Regs.TCR.bit.TSS = 0; //start Timer0 to catch runaway while loop

while(Msg_Flags.bit.spia_rx_rdy != 1){

if(Msg_Flags.bit.Timeout == 1){

SciaTx(String_err);

SciaTx(": SPI Timeout");

return;

}

}

CpuTimer0Regs.TCR.bit.TSS = 0; //stop Timer0 since while successful

CpuTimer0Regs.TCR.bit.TRB = 1; //reload Timer0

}

Data[i] = SpiaRegs.SPIRXBUF;

i++;

}

CS_High(CS);//raise CS to finish

SciaTxByte(BN);

i = n; //dummy transfer to clear build

//#endif

}