Greetings,

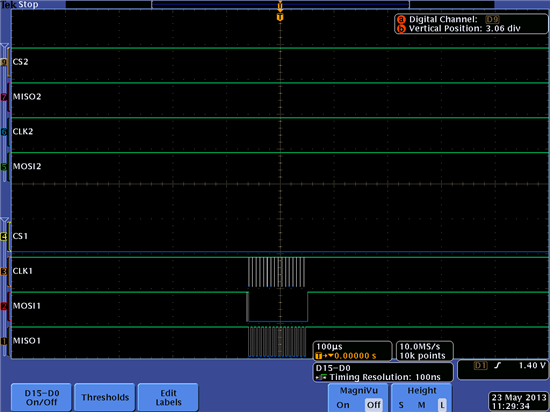

I am using the F28335 and I am not sure if I am initializing the SPI correctly to work for gpio ports 12,13, 14, and 15. Is this the correct way to do it? I can't seem to see any signals being sent out from these pins.

case 3:

if (strncmp(SPI_Mode, "MOSI",4)== 0){

// SciaTx("GPIO12");

GpioCtrlRegs.GPAPUD.bit.GPIO12 = 0; // Enable pull-up on GPIO12 (SPISIMOA)

GpioCtrlRegs.GPAQSEL1.bit.GPIO12 = 3; // Asynch input GPIO12 (SPISIMOA)

GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 1; // Configure GPIO12 as SPISIMOA

GpioCtrlRegs.GPADIR.bit.GPIO12 = 1; //set FRAM CS as out

}

else if (strncmp(SPI_Mode, "MISO",4)== 0){

// SciaTx("GPIO12");

GpioCtrlRegs.GPAPUD.bit.GPIO13 = 0; // Enable pull-up on GPIO13 (SPISOMIA)

GpioCtrlRegs.GPAQSEL1.bit.GPIO13 = 3; // Asynch input GPIO13 (SPISOMIA)

GpioCtrlRegs.GPAMUX1.bit.GPIO13 = 1; // Configure GPIO13 as SPISOMIA

}

else if (strncmp(SPI_Mode, "CLK=",4)== 0){

// SciaTx("GPIO14");

GpioCtrlRegs.GPAPUD.bit.GPIO14 = 0; // Enable pull-up on GPIO14 (SPICLKA)

GpioCtrlRegs.GPAQSEL1.bit.GPIO14 = 3; // Asynch input GPIO14 (SPICLKA)

GpioCtrlRegs.GPAMUX1.bit.GPIO14 = 1; // Configure GPIO14 as SPICLKA

GpioCtrlRegs.GPADIR.bit.GPIO14 = 1; //set FRAM CS as out

}

else if (strncmp(SPI_Mode, "CS=G",4)== 0){

// SciaTx("GPIO15");

GpioDataRegs.GPASET.bit.GPIO15 = 1; //pre-set FRAM CS high

GpioCtrlRegs.GPADIR.bit.GPIO15 = 1; //set FRAM CS as out

}