Hi, I have a problem with sine wave generated using simulink. I use DSP sine wave block from Signal Processing Blockset of simulink to generate discrete sine wave with the following setting:

Amplitude: [0.7*4 0.7*4 0.7*4]

Frequency: [50 50 50]

Phase offset: [0 4*pi/3 2*pi/3]

Sample Time: 1/1000

Sample per frame: 1

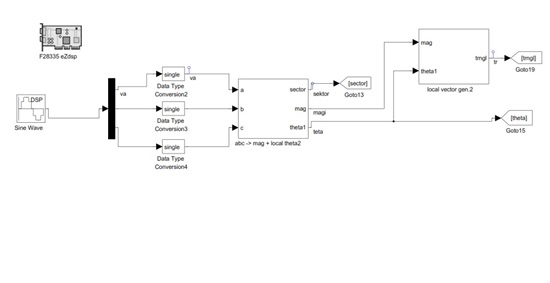

I attach snapshot part of my simulink model. I observed variable "va" which is refer to output of sine wave in the figure. Based on the setting of the sine wave source, "va" should be 50 Hz which is 0.02s/cycle. The problem here is "va" frequency is 0.4Hz which is 2.5s/cycle and should be 50Hz. Then to verify this problem, I complete the simulink block by producing signal low and high at digital output of the eZDSP at every cycle of sine wave.

This is the code generated from Simulink (e2etiQ1.c):

/*

* File: e2etiQ1.c

*

* Real-Time Workshop code generated for Simulink model e2etiQ1.

*

* Model version : 1.95

* Real-Time Workshop file version : 7.4 (R2009b) 29-Jun-2009

* Real-Time Workshop file generated on : Wed Nov 13 16:30:09 2013

* TLC version : 7.4 (Jul 14 2009)

* C/C++ source code generated on : Wed Nov 13 16:30:10 2013

*

* Target selection: ccslink_ert.tlc

* Embedded hardware selection: Texas Instruments->C2000

* Code generation objectives: Unspecified

* Validation result: Not run

*/

#include "e2etiQ1.h"

#include "e2etiQ1_private.h"

/* Block signals (auto storage) */

BlockIO_e2etiQ1 e2etiQ1_B;

/* Block states (auto storage) */

D_Work_e2etiQ1 e2etiQ1_DWork;

/* Real-time model */

RT_MODEL_e2etiQ1 e2etiQ1_M_;

RT_MODEL_e2etiQ1 *e2etiQ1_M = &e2etiQ1_M_;

static void rate_scheduler(void);

/*

* This function updates active task flag for each subrate.

* The function must be called at model base rate, hence the

* generated code self-manages all its subrates.

*/

static void rate_scheduler(void)

{

/* Compute which subrates run during the next base time step. Subrates

* are an integer multiple of the base rate counter. Therefore, the subtask

* counter is reset when it reaches its limit (zero means run).

*/

if (++(e2etiQ1_M->Timing.TaskCounters.TID[1]) > 999) {/* Sample time: [0.001s, 0.0s] */

e2etiQ1_M->Timing.TaskCounters.TID[1] = 0;

}

}

/* Model step function */

void e2etiQ1_step(int_T tid)

{

{

real32_T rtb_ComplextoMagnitudeAngle_o1;

real32_T rtb_Gain3;

real32_T rtb_thet;

if (e2etiQ1_M->Timing.TaskCounters.TID[1] == 0) {

/* S-Function (sdspsine2): '<Root>/Sine Wave' */

e2etiQ1_B.SineWave[0] = e2etiQ1_ConstP.SineWave_Values_Sine[(int32_T)

e2etiQ1_DWork.SineWave_TableIdx[0]];

e2etiQ1_DWork.SineWave_TableIdx[0] = e2etiQ1_DWork.SineWave_TableIdx[0] +

1U;

if (e2etiQ1_DWork.SineWave_TableIdx[0] >= 20U) {

e2etiQ1_DWork.SineWave_TableIdx[0] = 0U;

}

e2etiQ1_B.SineWave[1] = e2etiQ1_ConstP.SineWave_Values_Sine[20L + (int32_T)

e2etiQ1_DWork.SineWave_TableIdx[1]];

e2etiQ1_DWork.SineWave_TableIdx[1] = e2etiQ1_DWork.SineWave_TableIdx[1] +

1U;

if (e2etiQ1_DWork.SineWave_TableIdx[1] >= 20U) {

e2etiQ1_DWork.SineWave_TableIdx[1] = 0U;

}

e2etiQ1_B.SineWave[2] = e2etiQ1_ConstP.SineWave_Values_Sine[40L + (int32_T)

e2etiQ1_DWork.SineWave_TableIdx[2]];

e2etiQ1_DWork.SineWave_TableIdx[2] = e2etiQ1_DWork.SineWave_TableIdx[2] +

1U;

if (e2etiQ1_DWork.SineWave_TableIdx[2] >= 20U) {

e2etiQ1_DWork.SineWave_TableIdx[2] = 0U;

}

/* DataTypeConversion: '<Root>/Data Type Conversion2' */

e2etiQ1_B.va = e2etiQ1_B.SineWave[0];

}

/* RealImagToComplex: '<S2>/Real-Imag to Complex' incorporates:

* Gain: '<S2>/Gain1'

* Gain: '<S2>/Gain2'

* SignalConversion: '<S2>/TmpSignal ConversionAtGain1Inport1'

*/

rtb_Gain3 = (e2etiQ1_P.Gain1_Gain[0] * e2etiQ1_B.va + e2etiQ1_P.Gain1_Gain[1]

* e2etiQ1_B.SineWave[1]) + e2etiQ1_P.Gain1_Gain[2] *

e2etiQ1_B.SineWave[2];

rtb_thet = (e2etiQ1_P.Gain2_Gain[0] * e2etiQ1_B.va + e2etiQ1_P.Gain2_Gain[1]

* e2etiQ1_B.SineWave[1]) + e2etiQ1_P.Gain2_Gain[2] *

e2etiQ1_B.SineWave[2];

/* ComplexToMagnitudeAngle: '<S2>/Complex to Magnitude-Angle' */

rtb_ComplextoMagnitudeAngle_o1 = rt_hypot32_snf(rtb_Gain3, rtb_thet);

/* Gain: '<S2>/Gain3' */

rtb_Gain3 = e2etiQ1_P.Gain3_Gain * rt_atan232_snf(rtb_thet, rtb_Gain3);

/* Embedded MATLAB: '<S2>/3' */

/* Embedded MATLAB Function 'abc -> mag + local theta2/3': '<S4>:1' */

/* equations used in this mathlab function is based on Table I "A novel */

/* Neutral point stabilization technique using the information of output */

/* current polarities and voltage vector'by Katsutoshi Yamanaka, IEEE */

/* Industrial Application 2002 */

if ((real_T)rtb_Gain3 >= 150.0) {

/* '<S4>:1:10' */

/* '<S4>:1:11' */

rtb_thet = rtb_Gain3 - 120.0F;

} else if ((real_T)rtb_Gain3 < -150.0) {

/* '<S4>:1:13' */

/* '<S4>:1:14' */

rtb_thet = rtb_Gain3 + 240.0F;

} else {

/* '<S4>:1:19' */

rtb_thet = 0.0F;

}

/* Product: '<S2>/Product5' incorporates:

* Constant: '<S2>/Constant5'

* Constant: '<S7>/Constant'

* Constant: '<S8>/Constant'

* Logic: '<S2>/Logical Operator5'

* RelationalOperator: '<S7>/Compare'

* RelationalOperator: '<S8>/Compare'

*/

e2etiQ1_B.Product5 = (rtb_Gain3 >= e2etiQ1_P.Constant_Value_g) && (rtb_Gain3

< e2etiQ1_P.Constant_Value_j) ? e2etiQ1_P.Constant5_Value : 0.0;

/* Sum: '<S2>/Sum' incorporates:

* Constant: '<S10>/Constant'

* Constant: '<S11>/Constant'

* Constant: '<S12>/Constant'

* Constant: '<S13>/Constant'

* Constant: '<S14>/Constant'

* Constant: '<S15>/Constant'

* Constant: '<S16>/Constant'

* Constant: '<S17>/Constant'

* Constant: '<S18>/Constant'

* Constant: '<S2>/Constant'

* Constant: '<S2>/Constant1'

* Constant: '<S2>/Constant2'

* Constant: '<S2>/Constant3'

* Constant: '<S2>/Constant4'

* Constant: '<S5>/Constant'

* Constant: '<S6>/Constant'

* Constant: '<S9>/Constant'

* Logic: '<S2>/Logical Operator'

* Logic: '<S2>/Logical Operator1'

* Logic: '<S2>/Logical Operator2'

* Logic: '<S2>/Logical Operator3'

* Logic: '<S2>/Logical Operator4'

* Logic: '<S2>/Logical Operator6'

* Logic: '<S2>/Logical Operator7'

* Product: '<S2>/Product'

* Product: '<S2>/Product1'

* Product: '<S2>/Product2'

* Product: '<S2>/Product3'

* Product: '<S2>/Product4'

* RelationalOperator: '<S10>/Compare'

* RelationalOperator: '<S11>/Compare'

* RelationalOperator: '<S12>/Compare'

* RelationalOperator: '<S13>/Compare'

* RelationalOperator: '<S14>/Compare'

* RelationalOperator: '<S15>/Compare'

* RelationalOperator: '<S16>/Compare'

* RelationalOperator: '<S17>/Compare'

* RelationalOperator: '<S18>/Compare'

* RelationalOperator: '<S5>/Compare'

* RelationalOperator: '<S6>/Compare'

* RelationalOperator: '<S9>/Compare'

*/

e2etiQ1_B.sektor = (real_T)((((((real32_T)((rtb_Gain3 >=

e2etiQ1_P.Constant_Value_h) && (rtb_Gain3 < e2etiQ1_P.Constant_Value_c) ?

e2etiQ1_P.Constant_Value : 0.0) + (real32_T)((rtb_Gain3 >=

e2etiQ1_P.Constant_Value_n) && (rtb_Gain3 < e2etiQ1_P.Constant_Value_f) ?

e2etiQ1_P.Constant1_Value : 0.0)) + (real32_T)(((rtb_Gain3 >=

e2etiQ1_P.Constant_Value_o) && (rtb_Gain3 <= e2etiQ1_P.Constant_Value_k)) ||

((rtb_Gain3 >= e2etiQ1_P.Constant_Value_cd) &&

(rtb_Gain3 < e2etiQ1_P.Constant_Value_cq)) ?

e2etiQ1_P.Constant2_Value : 0.0)) + (real32_T)((rtb_Gain3 >=

e2etiQ1_P.Constant_Value_l) && (rtb_Gain3 < e2etiQ1_P.Constant_Value_hz) ?

e2etiQ1_P.Constant3_Value : 0.0)) + (real32_T)((rtb_Gain3 >=

e2etiQ1_P.Constant_Value_a) && (rtb_Gain3 < e2etiQ1_P.Constant_Value_e) ?

e2etiQ1_P.Constant4_Value : 0.0)) + (real32_T)e2etiQ1_B.Product5);

/* MultiPortSwitch: '<S2>/Multiport Switch' incorporates:

* Fcn: '<S2>/1'

* Fcn: '<S2>/2'

* Fcn: '<S2>/4'

* Fcn: '<S2>/5'

* Fcn: '<S2>/6'

*/

switch ((int16_T)e2etiQ1_B.sektor) {

case 1:

e2etiQ1_B.MultiportSwitch = rtb_Gain3;

break;

case 2:

e2etiQ1_B.MultiportSwitch = rtb_Gain3 - 60.0F;

break;

case 3:

e2etiQ1_B.MultiportSwitch = rtb_thet;

break;

case 4:

e2etiQ1_B.MultiportSwitch = rtb_Gain3 + 180.0F;

break;

case 5:

e2etiQ1_B.MultiportSwitch = rtb_Gain3 + 120.0F;

break;

default:

e2etiQ1_B.MultiportSwitch = rtb_Gain3 + 60.0F;

break;

}

/* Fcn: '<S3>/V_alfa' */

e2etiQ1_B.V_alfa = (real32_T)cos(e2etiQ1_B.MultiportSwitch * 3.141592741F /

180.0F) * rtb_ComplextoMagnitudeAngle_o1;

/* Fcn: '<S3>/V_beta' */

e2etiQ1_B.V_beta = (real32_T)sin(e2etiQ1_B.MultiportSwitch * 3.141592741F /

180.0F) * rtb_ComplextoMagnitudeAngle_o1;

/* Embedded MATLAB: '<S3>/Embedded MATLAB Function' */

/* Embedded MATLAB Function 'local vector gen.2/Embedded MATLAB Function': '<S19>:1' */

/* equations used in this mathlab function is based on Table I "A novel */

/* Neutral point stabilization technique using the information of output */

/* current polarities and voltage vector'by Katsutoshi Yamanaka, IEEE */

/* Indubestrial Application 2002 */

if (((real_T)e2etiQ1_B.V_alfa < 1.7320508075688772E+000) && ((real_T)

e2etiQ1_B.V_beta < 2.0)) {

/* '<S19>:1:9' */

/* '<S19>:1:12' */

if (e2etiQ1_B.V_beta > (-e2etiQ1_B.V_alfa) / 1.732050776E+000F + 2.0F) {

/* '<S19>:1:14' */

/* '<S19>:1:15' */

e2etiQ1_B.tr = 3.0F;

} else {

/* '<S19>:1:18' */

e2etiQ1_B.tr = 1.0F;

}

} else if (((real_T)e2etiQ1_B.V_alfa < 1.7320508075688772E+000) && ((real_T)

e2etiQ1_B.V_beta >= 2.0)) {

/* '<S19>:1:22' */

/* '<S19>:1:24' */

if (e2etiQ1_B.V_beta > e2etiQ1_B.V_alfa / 1.732050776E+000F + 2.0F) {

/* '<S19>:1:27' */

/* '<S19>:1:28' */

e2etiQ1_B.tr = 4.0F;

} else {

/* '<S19>:1:30' */

e2etiQ1_B.tr = 3.0F;

}

} else if ((real_T)e2etiQ1_B.V_alfa >= 1.7320508075688772E+000) {

/* '<S19>:1:34' */

/* '<S19>:1:35' */

e2etiQ1_B.tr = 2.0F;

} else {

/* '<S19>:1:40' */

e2etiQ1_B.tr = 0.0F;

}

}

/* Update absolute time for base rate */

/* The "clockTick0" counts the number of times the code of this task has

* been executed. The resolution of this integer timer is 1.0E-006, which is the step size

* of the task. Size of "clockTick0" ensures timer will not overflow during the

* application lifespan selected.

* Timer of this task consists of two 32 bit unsigned integers.

* The two integers represent the low bits Timing.clockTick0 and the high bits

* Timing.clockTickH0. When the low bit overflows to 0, the high bits increment.

*/

e2etiQ1_M->Timing.clockTick0++;

if (!e2etiQ1_M->Timing.clockTick0)

e2etiQ1_M->Timing.clockTickH0++;

rate_scheduler();

/* tid is required for a uniform function interface.

* Argument tid is not used in the function. */

UNUSED_PARAMETER(tid);

}

/* Model initialize function */

void e2etiQ1_initialize(boolean_T firstTime)

{

(void)firstTime;

/* Registration code */

/* initialize non-finites */

rt_InitInfAndNaN(sizeof(real_T));

/* initialize real-time model */

(void) memset((void *)e2etiQ1_M,0,

sizeof(RT_MODEL_e2etiQ1));

/* block I/O */

(void) memset(((void *) &e2etiQ1_B),0,

sizeof(BlockIO_e2etiQ1));

/* states (dwork) */

(void) memset((void *)&e2etiQ1_DWork, 0,

sizeof(D_Work_e2etiQ1));

/* Start for S-Function (sdspsine2): '<Root>/Sine Wave' */

/* Full-cycle Table lookup */

e2etiQ1_DWork.SineWave_TableIdx[0] = 0U;

e2etiQ1_DWork.SineWave_TableIdx[1] = 0U;

e2etiQ1_DWork.SineWave_TableIdx[2] = 0U;

{

real32_T currSampTime;

/* InitializeConditions for S-Function (sdspsine2): '<Root>/Sine Wave' */

/* This code only executes when block is re-enabled in an

enabled subsystem when the enabled subsystem states on

re-enabling are set to 'Reset' */

/* Catch up to present time on re-enable */

/* Full-cycle Table lookup */

currSampTime = (real32_T)(((e2etiQ1_M->Timing.clockTick0+

e2etiQ1_M->Timing.clockTickH0* 4294967296.0)) * 1.0E-006);

e2etiQ1_DWork.SineWave_TableIdx[0] = (uint16_T)((uint32_T)(currSampTime /

1.000000047E-003F + 0.5F) % (uint32_T)20U);

e2etiQ1_DWork.SineWave_TableIdx[1] = (uint16_T)((uint32_T)(currSampTime /

1.000000047E-003F + 0.5F) % (uint32_T)20U);

e2etiQ1_DWork.SineWave_TableIdx[2] = (uint16_T)((uint32_T)(currSampTime /

1.000000047E-003F + 0.5F) % (uint32_T)20U);

}

}

/* Model terminate function */

void e2etiQ1_terminate(void)

{

/* (no terminate code required) */

}

/*

* File trailer for Real-Time Workshop generated code.

*

* [EOF]

*/

and another file generated by Simulink (MW_c28xx_cls.c):

#include "DSP2833x_Device.h"

#include "DSP2833x_GlobalPrototypes.h"

#include "rtwtypes.h"

#include "e2etiQ1.h"

#include "e2etiQ1_private.h"

void rt_OneStep(void);

/*-----------------------------------------------------------------------------

* void config_schedulerTimer(void)

*

* Abstract:

* This function configures scheduler timer

*/

void config_schedulerTimer(void)

{

InitCpuTimers();

/* Configure CPU-Timer 0 to interrupt every 1.0E-006 sec. */

/* Parameters: Timer Pointer, CPU Freq in MHz, Period in usec. */

ConfigCpuTimer(&CpuTimer0, 150.0, 1.0E-006 * 1000000);

StartCpuTimer0();

}

void disableWatchdog(void)

{

int *WatchdogWDCR = (void *) 0x7029;

asm(" EALLOW ");

*WatchdogWDCR = 0x0068;

asm(" EDIS ");

}

interrupt void TINT0_isr(void)

{

volatile unsigned int PIEIER1_stack_save = PieCtrlRegs.PIEIER1.all;

PieCtrlRegs.PIEIER1.all &= ~64; //disable group1 lower/equal priority interrupts

asm(" RPT #5 || NOP"); //wait 5 cycles

IFR &= ~1; //eventually disable lower/equal priority pending interrupts

PieCtrlRegs.PIEACK.all = 1; //ACK to allow other interrupts from the same group to fire

IER |= 1;

EINT; //global interrupt enable

rt_OneStep();

DINT; // disable global interrupts during context switch, CPU will enable global interrupts after exiting ISR

PieCtrlRegs.PIEIER1.all = PIEIER1_stack_save;//restore PIEIER register that was modified

}

void enable_interrupts()

{

EALLOW;

PieVectTable.TINT0 = &TINT0_isr; // Hook interrupt to the ISR

EDIS;

PieCtrlRegs.PIEIER1.bit.INTx7 = 1; // Enable interrupt TINT0

IER |= M_INT1;

// Enable global Interrupts and higher priority real-time debug events:

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

}

void disable_interrupts()

{

IER &= M_INT1; // Disable Global INT1 (CPU Interrupt 1)

DINT; // Disable Global interrupt INTM

}

void init_board ()

{

InitSysCtrl();

EALLOW;

/* Perform additional configuration of the XTINF for speed up */

XintfRegs.XINTCNF2.bit.XTIMCLK = 0; // XTIMCLK=SYSCLKOUT/1

XintfRegs.XINTCNF2.bit.CLKOFF = 0; // XCLKOUT is enabled

XintfRegs.XINTCNF2.bit.CLKMODE = 0; // XCLKOUT = XTIMCLK

// Make sure write buffer is empty before configuring buffering depth

while (XintfRegs.XINTCNF2.bit.WLEVEL != 0) ;// poll the WLEVEL bit

XintfRegs.XINTCNF2.bit.WRBUFF = 0; // No write buffering

// Example: Assume Zone 7 is slow, so add additional BCYC cycles whenever

// switching from Zone 7 to another Zone. This will help avoid bus contention.

XintfRegs.XBANK.bit.BCYC = 3; // Add 7 cycles

XintfRegs.XBANK.bit.BANK = 3; // select zone 7

/* Zone 0 Configuration */

XintfRegs.XTIMING0.bit.X2TIMING = 0; // Timing scale factor = 1

XintfRegs.XTIMING0.bit.XSIZE = 3; // Always write as 11b

XintfRegs.XTIMING0.bit.READYMODE = 1;// XREADY is asynchronous

XintfRegs.XTIMING0.bit.USEREADY = 0; // Disable XREADY

XintfRegs.XTIMING0.bit.XRDLEAD = 1; // Read lead time

XintfRegs.XTIMING0.bit.XRDACTIVE = 2;// Read active time

XintfRegs.XTIMING0.bit.XRDTRAIL = 1; // Read trail time

XintfRegs.XTIMING0.bit.XWRLEAD = 1; // Write lead time

XintfRegs.XTIMING0.bit.XWRACTIVE = 2;// Write active time

XintfRegs.XTIMING0.bit.XWRTRAIL = 1; // Write trail time

/* Zone 6 Configuration */

XintfRegs.XTIMING6.bit.X2TIMING = 0; // Timing scale factor = 1

XintfRegs.XTIMING6.bit.XSIZE = 3; // Always write as 11b

XintfRegs.XTIMING6.bit.READYMODE = 1;// XREADY is asynchronous

XintfRegs.XTIMING6.bit.USEREADY = 0; // Disable XREADY

XintfRegs.XTIMING6.bit.XRDLEAD = 1; // Read lead time

XintfRegs.XTIMING6.bit.XRDACTIVE = 2;// Read active time

XintfRegs.XTIMING6.bit.XRDTRAIL = 1; // Read trail time

XintfRegs.XTIMING6.bit.XWRLEAD = 1; // Write lead time

XintfRegs.XTIMING6.bit.XWRACTIVE = 2;// Write active time

XintfRegs.XTIMING6.bit.XWRTRAIL = 1; // Write trail time

/* Zone 7 Configuration */

XintfRegs.XTIMING7.bit.X2TIMING = 0; // Timing scale factor = 1

XintfRegs.XTIMING7.bit.XSIZE = 3; // Always write as 11b

XintfRegs.XTIMING7.bit.READYMODE = 1;// XREADY is asynchronous

XintfRegs.XTIMING7.bit.USEREADY = 0; // Disable XREADY

XintfRegs.XTIMING7.bit.XRDLEAD = 1; // Read lead time

XintfRegs.XTIMING7.bit.XRDACTIVE = 2;// Read active time

XintfRegs.XTIMING7.bit.XRDTRAIL = 1; // Read trail time

XintfRegs.XTIMING7.bit.XWRLEAD = 1; // Write lead time

XintfRegs.XTIMING7.bit.XWRACTIVE = 2;// Write active time

XintfRegs.XTIMING7.bit.XWRTRAIL = 1; // Write trail time

EDIS;

InitXintf16Gpio();

/* Flush pipeline to ensure that the write is complete. Wait to be sure. */

asm(" RPT #6 || NOP");

/* Disable and clear all CPU interrupts */

DINT;

IER = 0x0000;

IFR = 0x0000;

InitPieCtrl();

InitPieVectTable();

/* initial SPI function.... */

InitCpuTimers();

/* initial GPIO qualification settings.... */

EALLOW;

GpioCtrlRegs.GPAQSEL1.all = 0U;

GpioCtrlRegs.GPAQSEL2.all = 0U;

GpioCtrlRegs.GPBQSEL1.all = 0U;

GpioCtrlRegs.GPBQSEL2.all = 0U;

EDIS;

}

void InitXintf16Gpio()

{

EALLOW;

GpioCtrlRegs.GPCMUX1.bit.GPIO64 = 3; // XD15

GpioCtrlRegs.GPCMUX1.bit.GPIO65 = 3; // XD14

GpioCtrlRegs.GPCMUX1.bit.GPIO66 = 3; // XD13

GpioCtrlRegs.GPCMUX1.bit.GPIO67 = 3; // XD12

GpioCtrlRegs.GPCMUX1.bit.GPIO68 = 3; // XD11

GpioCtrlRegs.GPCMUX1.bit.GPIO69 = 3; // XD10

GpioCtrlRegs.GPCMUX1.bit.GPIO70 = 3; // XD19

GpioCtrlRegs.GPCMUX1.bit.GPIO71 = 3; // XD8

GpioCtrlRegs.GPCMUX1.bit.GPIO72 = 3; // XD7

GpioCtrlRegs.GPCMUX1.bit.GPIO73 = 3; // XD6

GpioCtrlRegs.GPCMUX1.bit.GPIO74 = 3; // XD5

GpioCtrlRegs.GPCMUX1.bit.GPIO75 = 3; // XD4

GpioCtrlRegs.GPCMUX1.bit.GPIO76 = 3; // XD3

GpioCtrlRegs.GPCMUX1.bit.GPIO77 = 3; // XD2

GpioCtrlRegs.GPCMUX1.bit.GPIO78 = 3; // XD1

GpioCtrlRegs.GPCMUX1.bit.GPIO79 = 3; // XD0

GpioCtrlRegs.GPBMUX1.bit.GPIO40 = 3; // XA0/XWE1n

GpioCtrlRegs.GPBMUX1.bit.GPIO41 = 3; // XA1

GpioCtrlRegs.GPBMUX1.bit.GPIO42 = 3; // XA2

GpioCtrlRegs.GPBMUX1.bit.GPIO43 = 3; // XA3

GpioCtrlRegs.GPBMUX1.bit.GPIO44 = 3; // XA4

GpioCtrlRegs.GPBMUX1.bit.GPIO45 = 3; // XA5

GpioCtrlRegs.GPBMUX1.bit.GPIO46 = 3; // XA6

GpioCtrlRegs.GPBMUX1.bit.GPIO47 = 3; // XA7

GpioCtrlRegs.GPCMUX2.bit.GPIO80 = 3; // XA8

GpioCtrlRegs.GPCMUX2.bit.GPIO81 = 3; // XA9

GpioCtrlRegs.GPCMUX2.bit.GPIO82 = 3; // XA10

GpioCtrlRegs.GPCMUX2.bit.GPIO83 = 3; // XA11

GpioCtrlRegs.GPCMUX2.bit.GPIO84 = 3; // XA12

GpioCtrlRegs.GPCMUX2.bit.GPIO85 = 3; // XA13

GpioCtrlRegs.GPCMUX2.bit.GPIO86 = 3; // XA14

GpioCtrlRegs.GPCMUX2.bit.GPIO87 = 3; // XA15

GpioCtrlRegs.GPBMUX1.bit.GPIO39 = 3; // XA16

GpioCtrlRegs.GPAMUX2.bit.GPIO31 = 3; // XA17

GpioCtrlRegs.GPAMUX2.bit.GPIO30 = 3; // XA18

GpioCtrlRegs.GPAMUX2.bit.GPIO29 = 3; // XA19

GpioCtrlRegs.GPBMUX1.bit.GPIO34 = 3; // XREADY

GpioCtrlRegs.GPBMUX1.bit.GPIO35 = 3; // XRNW

GpioCtrlRegs.GPBMUX1.bit.GPIO38 = 3; // XWE0

GpioCtrlRegs.GPBMUX1.bit.GPIO36 = 3; // XZCS0

GpioCtrlRegs.GPBMUX1.bit.GPIO37 = 3; // XZCS7

GpioCtrlRegs.GPAMUX2.bit.GPIO28 = 3; // XZCS6

EDIS;

}

Simulink also create another c-files..I will place here if it will help me to solve this problem.

I think Matlab create wrong code or I don't have enough understanding to use simulink with DSP?

If the code generated can be modified to operate properly, do anyone have suggestion?

Thank you...

-madie-