We are pretty far in programming our product, which is based on Control card F28M35. We have working Ethernet, USB, and serial links, C28 is controlling our system. We have a serial command to reset controller, and it uses WDT as recommended. It worked just fine with Silicon Rev 0 chip (marked X).

Recently we got a few newer Control Cards with Silicon Rev 1 chip on them, and this WDT restart does not work on ALL of them - processor does not restart. However, it starts normally after power up.

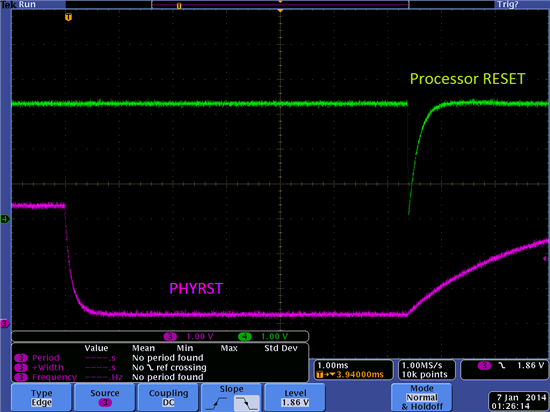

Same exact program works fine (restarts) on silicon 0. If look with scope on Reset line of silicon 0 chip, one can see single reset pulse, with sharp drop and slower rise, when WDT gets triggered.

On silicon 1 new card, if look with scope on Reset line, one can see pulses, period 1.24ms, with sharp drop and slower rise, same shape as a single pulse. Processor seems to stuck in the ROM BOOT area 0x0100xxxx.

We use BOOT FROM FLASH, where:

Signals on "BOOT" SW1 when processor held at reset: reset line is 0

SW1.1 (ON ) GPIO 34 =logic 0 (~0.2V)

SW1.2 (OFF) GPIO 35 =logic 1 (~3V)

SW1.3 (OFF) GPIO 47 =logic 1 (~3V)

SW1.4 (OFF) GPI0 43 =logic 1 (~3V)

Further investigation shows: IF THERE IS JUMPER or on Concerto card between J12.6 and J8.6 (which is needed for Ethernet to work, signal M3_MII_RXDV) new board does not restart. NOTE: this signal is mapped to GPIO_43 pin needed in BOOT choice.

Processor does not restart even if bring RESET line to 0 and release; it only restarts when power - cycled.

Other way to perform a restart: the M3_MII_PhyRSTn must be brought LOW ! (J9.6 pin to ground, or PJ7_GPIO63 port line if jumper J9.6-J13.6 is installed). Jumping this line to ground kills reset pulses and deliver a successful restart.

Thus, I suspect that the trio:

a) J12.6-to J8.6 – connection

b) property of the U17 pin #26 (RX_DV) of the LAN8710AI-EZK chip

c) TOGETHER WITH SOMETHING NEW IN F28M35 SILICON 1 chip

disturb GPIO_43 line during restart (which supposed to be logic 1) so BOOT is actually directed somewhere but not to FLASH, hangs there 1.2 ms and returns to reset again.

If reset line of U17 chip is activated (shorted to GND), its pin#26 property changes this allowing proper recognition of BOOT lines, and processor reboots.

I tried skipping initialization of Ethernet lines (function EthernetPinsSetup(), but does not help – reset pulses are there, processor stuck in ROM BOOT area 0x0100xxxx. Setting J7_GPIO63 to GPIO mode and send 0 to U17 just before WDT resets processor does not help either.

Any ideas what was changed in silicon 1 and how to restart processor now if Ethernet is absolutely needed?

Igor