Hi everybody,

I have an issue with the behaviour of the digital comparator event 2 cycle by cycle tripping event. In our system, we use this comparator to stop CBC a PWM when the value configured into the DAC his reach.

I made multiple trial without any issue, but when I reach a particular open time of my PWM the PWM trip zone CBC seems to discard my comparator output value.

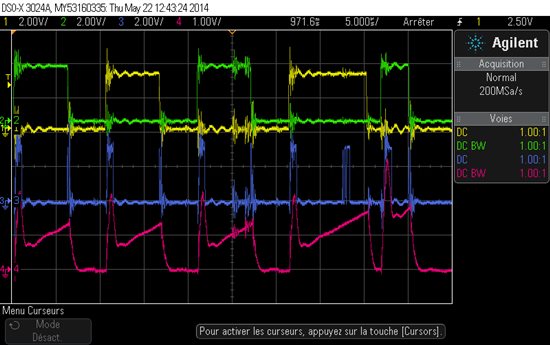

I took the picture below to help understanding my issues

CH1: Gate right top

CH2: Gate left top

CH3: Comparator 2 output signal

CH4: Comparator 2 non inverting input signal

As I observe on the fourth event on the channel 4, the comparator output signal is force to 1 when the comparator non inverting input has reach my set value, but I observe no effect on the corresponding PWM (CH1). That error generate an instability in our system.

I validate all configuration and for this moment they seems to be okay, but if you need more detail about the software configuration, just ask me!

Any body can help me with this particular issue??

Marc-Olivier Brassard, Jr. Eng.

Electronic designer