Hi

I'm using the dual sequencer mode on TMS320F28335 ADC.

SOC is triggered by ePWM:

Sequencer1: SOCA from ePWM1 when CTR=PRD

Sequencer2: SOCB from ePWM2 when CTR=PRD

After EOC (end of conversion) an interrupt is triggered:

INT_SEQ1 for sequencer 1

INT_SEQ2 for sequencer 2

Because I want to use oversampling on SEQ1 I retrigger SEQ1 within INT_SEQ1

When I do this it corrupts INT_SEQ2 periodically which means that INT_SEQ2 is missed sometimes or occurs multiple times (a counter variable within INT_SEQ2 shows that INT_SEQ2 is called again when I reenable interrupts before ISR is finished).

If ePWM frequencies are exactly identical then there is no problem.

How is it possible that SEQ1 influences SEQ2 interrupt in this way?

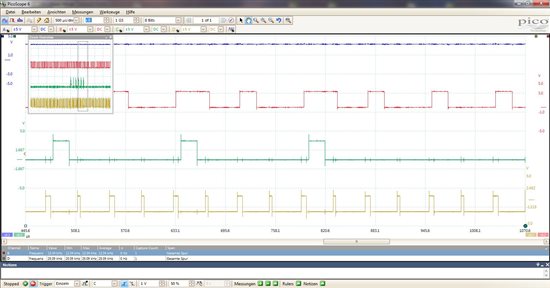

Attached you find a small program (CCS V5.5, Code Generation Tools V6.20.00) which shows the timing on three output pins. Also attached you find the actual timing output:

Blue: please ignore

Red: High within INT_SEQ2

Green: should never occurr: high within INT_SEQ2 if called a second time

Yellow: toggles each time INT_SEQ1 is called

Thanks in advance for our support!

Markus