Hi everybody,

I have developped a perfectly working application on a C28346 a year or so ago but the lack of internal non-volatile memory and the only available package being BGA, I am looking for downgrading to a F28335.

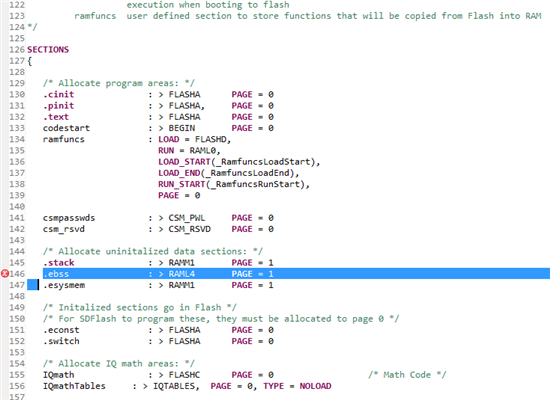

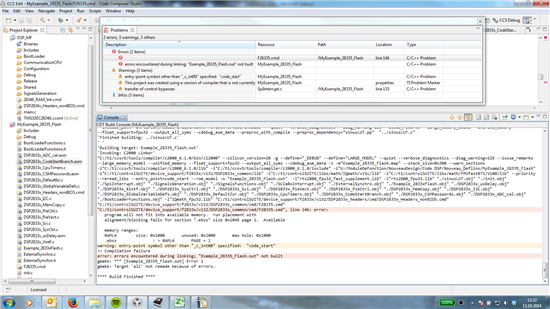

My first impression was that it should be pretty easy. Seems I was wrong: I have been on it for 2 days and haven't make a single step to have something working. I keep getting the error #10099-D about not having enough memory space. Seems strange to me since the application is not that big, especially for a device such the F28335.

Could anyone indicate me a reference which would describe the main steps for the downgrade? Or am I missing something really simple?

Best regards,

Christian