Hi there,

I'm new to TMS320F28xxx microprocessors and currently busy to develop the I2C part. In this matter a serial 256kBit EEPROM (slave) shall be partially read out.

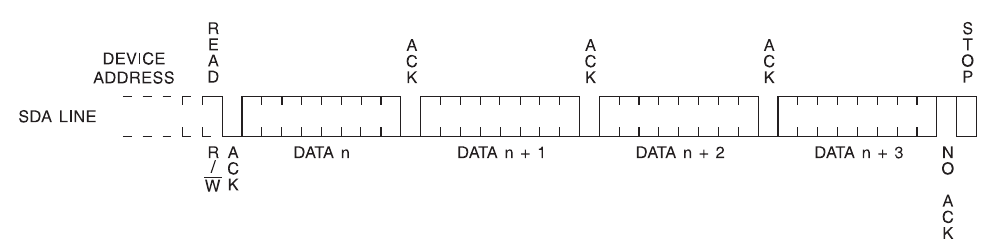

My question is if it is possible to read 80 byte with one read instruction a so far called sequential read (I'd like to call it burst read). The sequential read is not a FIFO read. With FIFO enabled I can read 4 byte with one read operation (more is not possible in FIFO mode). To get more than 4 byte at once I want to use the sequential read = no FIFO mode. In this diagram below are only 4 data bytes shown but can be many more.

The program code works as expected (checked out with DSO, see link below) but how can I read/copy the data from I2CDRR to memory at the right time, thus when an ACK is transmitted? I'm sure that DATA n until DATA n+x will be available in I2CDRR but how can I detect when the transfer in complete thus when the master (F28027) sends an ACK? Should an interrupt be triggered at that time or is it possible by polling a register bit? I've tried both but without success. When an NACK was sent an interrupt is triggered but how to detect an ACK? I suppose that this kind of I2C operation is not supported by F28027, isn't it?

The DSO measument shows the beginning (the first 4 data bytes) of the 80 bytes data read from EEPROM. The sequence is

START - dev. address write (0x50) - ACK - E² Hi-address (0x12) - ACK - E² Lo-address (0x34) - ACK - (RE)START - dev. address read (0x51) - ACK - DATA 1 (0xFF) - ACK - DATA 2 (0xFF) - ACK - DATA 3 (0xFF) - ACK - DATA 4 (0xFF) - ACK - DATA 5 .... (not shown)

http://phirma.kgenius.fastmail.com.au/home/pix/I2C-2.png

I hope someone could help me in this matter.