Now I use 28335's MCBSP DMA to receive data from a ADC(ADAR7251), there are 2 channels data on ADC output line, transfer format is shown in figures. a data array A[2048] is used to store the ADC data:

DATA1[0] -- CH1

DATA1[1] -- CH2

DATA1[2] -- CH1

DATA1[3] -- CH2

…

DATA1[2046] -- CH1

DATA1[2047] -- CH2

sometime I found the data is stored as

DATA1[0] -- CH2

DATA1[1] -- CH1

DATA1[2] -- CH2

DATA1[3] -- CH1

…

DATA1[2046] -- CH2

DATA1[2047] -- CH1

so I can not serperate ch1's data and ch2's data, what the problems ? my MCBSP_DMA configuration code are as following

static void Mcbspa_Init(Mcbsp_CfgType Mcbspa_Cfg)

{

InitMcbspaGpio();

McbspaRegs.SPCR2.all=0x0000;

McbspaRegs.MFFINT.all=0x0; // Disable all interrupts

McbspaRegs.RCR2.bit.RPHASE = 0;

McbspaRegs.RCR1.bit.RWDLEN1 = 2;

McbspaRegs.RCR2.bit.RDATDLY = 0;

McbspaRegs.XCR2.bit.XDATDLY = 0;

McbspaRegs.RCR1.bit.RFRLEN1 = 1;

McbspaRegs.XCR1.bit.XFRLEN1 = 0; // Transmit frame length 1 (1 to 128 words)

McbspaRegs.PCR.bit.SCLKME = 0;

McbspaRegs.SRGR2.bit.CLKSM = 1;

McbspaRegs.SRGR1.bit.CLKGDV = 0; // CLKG frequency = LSPCLK/(CLKGDV+1)

McbspaRegs.SRGR2.bit.FPER = 0; // FPER = 32 CLKG periods

McbspaRegs.SRGR1.bit.FWID = 0; // Frame Width = 1 CLKG period

McbspaRegs.PCR.bit.FSRM = 0; McbspaRegs.PCR.bit.FSRP = 0;

McbspaRegs.PCR.bit.CLKRM = 0; McbspaRegs.PCR.bit.CLKRP = 0;

McbspaRegs.SPCR2.bit.GRST = 1;

delay_loop();

McbspaRegs.SPCR2.bit.XRST= 1;

McbspaRegs.SPCR1.bit.RRST = 1;

McbspaRegs.SPCR2.bit.FRST = 1;

}

void Mcbspa_RDmaInit(void)

{

EALLOW;

DmaRegs.CH2.MODE.bit.CHINTE = 0; // disable DMA ch2 interrupt EDIS;

DMACH2BurstConfig(0, 0, 0);

DMACH2TransferConfig((Uint16)2048 -1, 0, 1);

DMACH2AddrConfig((int16*)(&ADC_DMA_Rising1_OUT0_Buf[0]),&McbspaRegs.DRR1.all);

DMACH2WrapConfig(0xFFFF, 0, 0xFFFF, 0);

DMACH2ModeConfig((Uint16)DMA_MREVTA, 1, 0, 0, 0, 0, 0,SIXTEEN_BIT, 1,1);

EALLOW;

PieVectTable.DINTCH2 = &Local_DMA_INTCH2_ISR;

EDIS;

IER |= M_INT7; PieCtrlRegs.PIEIER7.bit.INTx2 = 1;

}

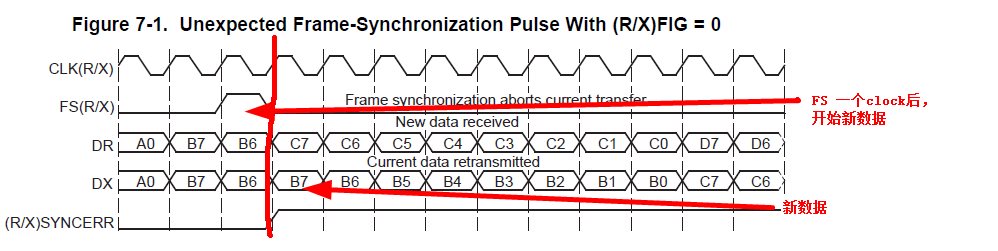

note: frame syn signal is pulse in Figure41