Hi,

My c28 flash code run in Share RAM, it can successfully erase, verify, but it can't program and verify the flash using F021.

API lib: F021_API_C28x.lib

oReturnCheck = Fapi_issueProgrammingCommand((uint32 *)flashAddrCtr, ramData+ramAddrCtr,

8, 0, 0, Fapi_AutoEccGeneration);

oReturnCheck returns with success,

oFlashStatus = Fapi_getFsmStatus(); oFlashStatus return 0x00001010;

oReturnCheck = Fapi_doVerify((uint32 *)flashAddrCtr, 4, ramData32+ramAddrCtr/2, &oFlashStatusWord);

returns failed (this is correct).

My question:

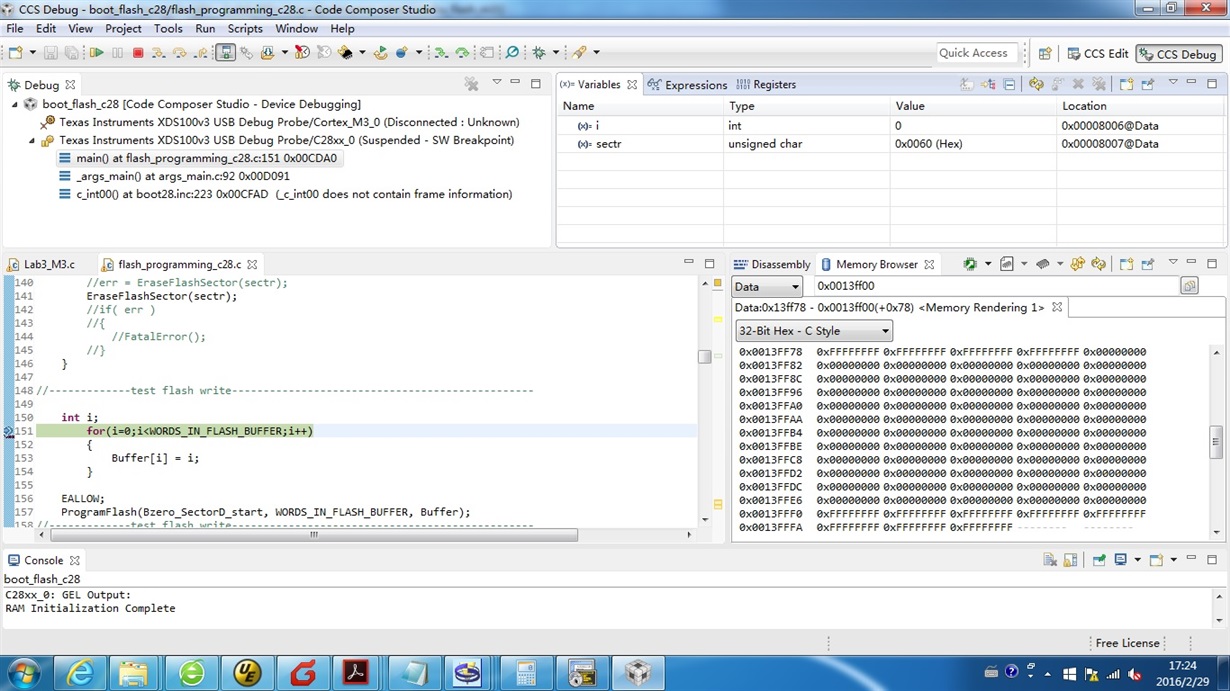

Please refer to the following subroutine code, cmd file and map file.

1, c28 program flash fail,What can go wrong?

2, If M3 use IPCLiteMtoCBootBranch(ADDRESS) to boot C28 form share RAM, What is the address location in this code?

subroutine:

uint32 ProgramFlash(uint32 flashStartAddr, uint16 psize, uint16 * ramData)

{

Fapi_StatusType oReturnCheck = Fapi_Status_Success; //Fapi status/error after calling an Fapi function

Fapi_FlashStatusWordType oFlashStatusWord; //Fapi status after burn check

volatile Fapi_FlashStatusType oFlashStatus;

uint32 *ramData32 = (uint32 *)ramData;

uint32 flashAddrCtr = 0;

uint16 ramAddrCtr = 0;

//Check flashStartAddr is a multiple of 16:

if( flashStartAddr & 0x00000007 != 0 )

{

return FLASH_BURN_ADDR_ERROR;

}

//Check to make sure size is a multiple of 8:

if( psize % 8 != 0 )

{

return FLASH_BURN_SIZE_ERROR;

}

for(ramAddrCtr=0, flashAddrCtr = flashStartAddr;

(flashAddrCtr < (flashStartAddr + psize)) && (oReturnCheck == Fapi_Status_Success);

ramAddrCtr += 8, flashAddrCtr += 8)

{

oReturnCheck = Fapi_issueProgrammingCommand((uint32 *)flashAddrCtr, ramData+ramAddrCtr,

8,

0,

0,

Fapi_AutoEccGeneration);

while(Fapi_checkFsmForReady() == Fapi_Status_FsmBusy){}

if(oReturnCheck != Fapi_Status_Success)

{

return (F021_ERROR_BASE + oReturnCheck);

}

//oFlashStatus = Fapi_getFsmStatus();

oReturnCheck = Fapi_doVerify((uint32 *)flashAddrCtr,

4,

ramData32+ramAddrCtr/2,

&oFlashStatusWord);

if(oReturnCheck != Fapi_Status_Success)

{

return (F021_ERROR_BASE + oReturnCheck);

}

}

return NO_ERROR;

}

cmd file:

/*

//###########################################################################

// FILE: F28M35x_generic_C28_FLASH.cmd

// TITLE: Linker Command File For all F28M35x devices

//###########################################################################

// $TI Release: F28M35x Support Library v207 $

// $Release Date: Mon Sep 21 16:49:54 CDT 2015 $

// $Copyright: Copyright (C) 2011-2015 Texas Instruments Incorporated -

// http://www.ti.com/ ALL RIGHTS RESERVED $

//###########################################################################

*/

/* ======================================================

// For Code Composer Studio V2.2 and later

// ---------------------------------------

// In addition to this memory linker command file,

// add the header linker command file directly to the project.

// The header linker command file is required to link the

// peripheral structures to the proper locations within

// the memory map.

// The header linker files are found in <base>\F28M35x_headers\cmd

// For BIOS applications add: F28M35x_Headers_BIOS.cmd

// For nonBIOS applications add: F28M35x_Headers_nonBIOS.cmd

========================================================= */

/* Define the memory block start/length for the F28M35x

PAGE 0 will be used to organize program sections

PAGE 1 will be used to organize data sections

Notes:

Memory blocks on F28M35x are uniform (ie same

physical memory) in both PAGE 0 and PAGE 1.

That is the same memory region should not be

defined for both PAGE 0 and PAGE 1.

Doing so will result in corruption of program

and/or data.

Contiguous SARAM memory blocks or flash sectors can be

be combined if required to create a larger memory block.

*/

MEMORY

{

PAGE 0: /* Program Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE1 for data allocation */

RAMS0 : origin = 0x00C000, length = 0x006000 /* on-chip Shared RAM block S0-S5*/

FLASH : origin = 0x100000, length = 0x3FF80 /* on-chip FLASH */

CSM_RSVD : origin = 0x13FF80, length = 0x000070 /* Part of FLASHA. Program with all 0x0000 when CSM is in use. */

BEGIN : origin = 0x13FFF0, length = 0x000002 /* Part of FLASHA. Used for "boot to Flash" bootloader mode. */

FLASH_EXE_ONLY_P0 : origin = 0x13FFF2, length = 0x000002 /* Part of FLASHA. Flash execute only locations in FLASHA */

ECSL_PWL_P0 : origin = 0x13FFF4, length = 0x000004 /* Part of FLASHA. ECSL password locations in FLASHA */

CSM_PWL_P0 : origin = 0x13FFF8, length = 0x000008 /* Part of FLASHA. CSM password locations in FLASHA */

FPUTABLES : origin = 0x3FD258, length = 0x0006A0 /* FPU Tables in Boot ROM */

IQTABLES : origin = 0x3FD8F8, length = 0x000B50 /* IQ Math Tables in Boot ROM */

IQTABLES2 : origin = 0x3FE448, length = 0x00008C /* IQ Math Tables in Boot ROM */

IQTABLES3 : origin = 0x3FE4D4, length = 0x0000AA /* IQ Math Tables in Boot ROM */

BOOTROM : origin = 0x3FEDA8, length = 0x001200 /* Boot ROM */

PIEMISHNDLR : origin = 0x3FFFBE, length = 0x000002 /* part of boot ROM */

RESET : origin = 0x3FFFC0, length = 0x000002 /* part of boot ROM */

VECTORS : origin = 0x3FFFC2, length = 0x00003E /* part of boot ROM */

PAGE 1 : /* Data Memory */

/* Memory (RAM/FLASH/OTP) blocks can be moved to PAGE0 for program allocation */

/* Registers remain on PAGE1 */

BOOT_RSVD : origin = 0x000000, length = 0x000050 /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x000050, length = 0x0003B0 /* on-chip RAM block M0 */

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAML0 : origin = 0x008000, length = 0x004000 /* on-chip RAM block L0 */

RAMS6 : origin = 0x012000, length = 0x001000 /* on-chip Shared RAM block S7 */

RAMS7 : origin = 0x013000, length = 0x001000 /* on-chip Shared RAM block S7 */

CTOMRAM : origin = 0x03F800, length = 0x000380 /* C28 to M3 Message RAM */

MTOCRAM : origin = 0x03FC00, length = 0x000380 /* M3 to C28 Message RAM */

}

/* Allocate sections to memory blocks.

Note:

codestart user defined section in DSP28_CodeStartBranch.asm used to redirect code

execution when booting to flash

ramfuncs user defined section to store functions that will be copied from Flash into RAM

*/

SECTIONS

{

/* Allocate program areas: */

.cinit : > RAMS0 PAGE = 0

.pinit : > RAMS0 PAGE = 0

.text : > RAMS0 PAGE = 0

codestart : > RAMS0 PAGE = 0

/*

GROUP

{

ramfuncs

{ -l F021_API_C28x.lib}

} LOAD = RAMS0,

RUN = RAML0,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_SIZE(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

PAGE = 1

*/

flashexeonly : > FLASH_EXE_ONLY_P0 PAGE = 0 /*RAMS0 PAGE = 1*/

ecslpasswds : > ECSL_PWL_P0 PAGE = 0

csmpasswds : > CSM_PWL_P0 PAGE = 0

csm_rsvd : > CSM_RSVD PAGE = 0

/* The following section definitions are required when using the IPC API Drivers */

GROUP : > CTOMRAM, PAGE = 1

{

PUTBUFFER

PUTWRITEIDX

GETREADIDX

}

GROUP : > MTOCRAM, PAGE = 1

{

GETBUFFER : TYPE = DSECT

GETWRITEIDX : TYPE = DSECT

PUTREADIDX : TYPE = DSECT

}

/* Allocate uninitalized data sections: */

.stack : > RAML0 PAGE = 1

.ebss : > RAMS0 PAGE = 0

.esysmem : > RAMS0 PAGE = 0

/* Initalized sections go in Flash */

/* For SDFlash to program these, they must be allocated to page 0 */

.econst : > RAMS0 PAGE = 0

.switch : > RAMS0 PAGE = 0

/* Allocate IQ math areas: */

IQmath : > RAMS0 PAGE = 0 /* Math Code */

IQmathTables : > IQTABLES, PAGE = 0, TYPE = NOLOAD

/* Allocate FPU math areas: */

FPUmathTables : > FPUTABLES, PAGE = 0, TYPE = NOLOAD

/* DMARAML2 : > RAML2, PAGE = 1

DMARAML3 : > RAML3, PAGE = 1

*/

/* Uncomment the section below if calling the IQNexp() or IQexp()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables2 : > IQTABLES2, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNexpTable.obj> (IQmathTablesRam)

}

*/

/* Uncomment the section below if calling the IQNasin() or IQasin()

functions from the IQMath.lib library in order to utilize the

relevant IQ Math table in Boot ROM (This saves space and Boot ROM

is 1 wait-state). If this section is not uncommented, IQmathTables2

will be loaded into other memory (SARAM, Flash, etc.) and will take

up space, but 0 wait-state is possible.

*/

/*

IQmathTables3 : > IQTABLES3, PAGE = 0, TYPE = NOLOAD

{

IQmath.lib<IQNasinTable.obj> (IQmathTablesRam)

}

*/

/* .reset is a standard section used by the compiler. It contains the */

/* the address of the start of _c_int00 for C Code. /*

/* When using the boot ROM this section and the CPU vector */

/* table is not needed. Thus the default type is set here to */

/* DSECT */

.reset : > RESET, PAGE = 0, TYPE = DSECT

vectors : > VECTORS PAGE = 0, TYPE = DSECT

}

/*

*/

map file:

******************************************************************************

TMS320C2000 Linker PC v6.4.6

******************************************************************************

>> Linked Tue Feb 23 17:56:45 2016

OUTPUT FILE NAME: <flash_programming_c28.out>

ENTRY POINT SYMBOL: "code_start" address: 0000e28a

MEMORY CONFIGURATION

name origin length used unused attr fill

---------------------- -------- --------- -------- -------- ---- --------

PAGE 0:

RAMS0 0000c000 00006000 0000228b 00003d75 RWIX

FLASH 00100000 0003ff80 00000000 0003ff80 RWIX

CSM_RSVD 0013ff80 00000070 00000070 00000000 RWIX

BEGIN 0013fff0 00000002 00000000 00000002 RWIX

FLASH_EXE_ONLY_P0 0013fff2 00000002 00000002 00000000 RWIX

ECSL_PWL_P0 0013fff4 00000004 00000004 00000000 RWIX

CSM_PWL_P0 0013fff8 00000008 00000008 00000000 RWIX

FPUTABLES 003fd258 000006a0 00000000 000006a0 RWIX

IQTABLES 003fd8f8 00000b50 00000000 00000b50 RWIX

IQTABLES2 003fe448 0000008c 00000000 0000008c RWIX

IQTABLES3 003fe4d4 000000aa 00000000 000000aa RWIX

BOOTROM 003feda8 00001200 00000000 00001200 RWIX

PIEMISHNDLR 003fffbe 00000002 00000000 00000002 RWIX

RESET 003fffc0 00000002 00000000 00000002 RWIX

VECTORS 003fffc2 0000003e 00000000 0000003e RWIX

PAGE 1:

BOOT_RSVD 00000000 00000050 00000050 00000000 RWIX

RAMM0 00000050 000003b0 000003b0 00000000 RWIX

RAMM1 00000400 00000400 00000400 00000000 RWIX

RAML0 00008000 00004000 0000084b 000037b5 RWIX

RAMS6 00012000 00001000 00000000 00001000 RWIX

RAMS7 00013000 00001000 00000000 00001000 RWIX

CTOMRAM 0003f800 00000380 00000000 00000380 RWIX

MTOCRAM 0003fc00 00000380 00000000 00000380 RWIX

SECTION ALLOCATION MAP

output attributes/

section page origin length input sections

-------- ---- ---------- ---------- ----------------

.text 0 0000c000 000010d1

0000c000 00000334 F021_API_C28x.lib : FlashStateMachine.obj (.text)

0000c334 000002dc : Read.obj (.text)

0000c610 000001c8 : Program.obj (.text)

0000c7d8 000001ae F28M35x_DefaultIsr.obj (.text:retain)

0000c986 00000180 F28M35x_SysCtrl.obj (.text)

0000cb06 000000f6 F021_API_C28x.lib : Info.obj (.text)

0000cbfc 000000da C28_flash.obj (.text)

0000ccd6 000000aa F021_API_C28x.lib : Utilities.obj (.text)

0000cd80 0000008c flash_programming_c28.obj (.text)

0000ce0c 0000007b F021_API_C28x.lib : BlankCheck.obj (.text)

0000ce87 00000078 Fapi_UserDefinedFunctions.obj (.text)

0000ceff 00000071 F021_API_C28x.lib : FlashStateMachine.obj (.text)

0000cf70 00000044 rts2800_ml.lib : boot.obj (.text)

0000cfb4 00000034 F021_API_C28x.lib : Init.obj (.text)

0000cfe8 0000002d F28M35x_PieCtrl.obj (.text)

0000d015 0000002b F021_API_C28x.lib : Async.obj (.text)

0000d040 00000020 F28M35x_PieVect.obj (.text)

0000d060 0000001e F021_API_C28x.lib : Verify.obj (.text)

0000d07e 00000019 rts2800_ml.lib : args_main.obj (.text)

0000d097 00000019 : exit.obj (.text)

0000d0b0 00000018 : ll_aox.obj (.text)

0000d0c8 00000009 : _lock.obj (.text)

.ebss 0 0000d0d2 0000106e UNINITIALIZED

0000d0d2 0000000c F021_API_C28x.lib : Init.obj (.ebss)

0000d0de 00000004 rts2800_ml.lib : exit.obj (.ebss)

0000d0e2 00000002 : _lock.obj (.ebss:__lock)

0000d0e4 00000002 : _lock.obj (.ebss:__unlock)

0000d0e6 0000001a --HOLE--

0000d100 00001040 flash_programming_c28.obj (.ebss)

.econst 0 0000e140 0000012a

0000e140 00000100 F28M35x_PieVect.obj (.econst)

0000e240 0000001c C28_flash.obj (.econst:_SectorAddress)

0000e25c 0000000e C28_flash.obj (.econst:_SectorLength)

.cinit 0 0000e26a 00000020

0000e26a 0000000a flash_programming_c28.obj (.cinit)

0000e274 0000000a rts2800_ml.lib : exit.obj (.cinit)

0000e27e 00000005 : _lock.obj (.cinit:__lock)

0000e283 00000005 : _lock.obj (.cinit:__unlock)

0000e288 00000002 --HOLE-- [fill = 0]

.pinit 0 0000c000 00000000 UNINITIALIZED

codestart

* 0 0000e28a 00000002

0000e28a 00000002 F28M35x_CodeStartBranch.obj (codestart)

csm_rsvd 0 0013ff80 00000070

0013ff80 00000070 F28M35x_CSMPasswords.obj (csm_rsvd)

flashexeonly

* 0 0013fff2 00000002

0013fff2 00000002 F28M35x_CSMPasswords.obj (flashexeonly)

ecslpasswds

* 0 0013fff4 00000004

0013fff4 00000004 F28M35x_CSMPasswords.obj (ecslpasswds)

csmpasswds

* 0 0013fff8 00000008

0013fff8 00000008 F28M35x_CSMPasswords.obj (csmpasswds)

GETBUFFER

* 0 0003fc00 00000000 DSECT

GETWRITEIDX

* 0 0003fc00 00000000 DSECT

PUTREADIDX

* 0 0003fc00 00000000 DSECT

.stack 1 00008000 00000100 UNINITIALIZED

00008000 00000100 --HOLE--

.reset 0 003fffc0 00000002 DSECT

003fffc0 00000002 rts2800_ml.lib : boot.obj (.reset)

vectors 0 003fffc2 00000000 DSECT

Adc1RegsFile

* 1 00000000 00000050 UNINITIALIZED

00000000 00000050 F28M35x_GlobalVariableDefs.obj (Adc1RegsFile)

FlashEccRegsFile

* 1 00000050 00000024 UNINITIALIZED

00000050 00000024 F28M35x_GlobalVariableDefs.obj (FlashEccRegsFile)

EpiRegsFile

* 1 00000074 0000000c UNINITIALIZED

00000074 0000000c F28M35x_GlobalVariableDefs.obj (EpiRegsFile)

FlashCtrlRegsFile

* 1 00000080 00000182 UNINITIALIZED

00000080 00000182 F28M35x_GlobalVariableDefs.obj (FlashCtrlRegsFile)

RAMErrRegsFile

* 1 00000202 0000003e UNINITIALIZED

00000202 0000003e F28M35x_GlobalVariableDefs.obj (RAMErrRegsFile)

PieVectTableCopyFile

* 1 00000240 00000100 UNINITIALIZED

00000240 00000100 F28M35x_GlobalVariableDefs.obj (PieVectTableCopyFile)

EPwm1RegsFile

* 1 00000340 00000080 UNINITIALIZED

00000340 00000080 F28M35x_GlobalVariableDefs.obj (EPwm1RegsFile)

CtoMIpcRegsFile

* 1 000003c0 00000040 UNINITIALIZED

000003c0 00000040 F28M35x_GlobalVariableDefs.obj (CtoMIpcRegsFile)

PieVectTableFile

* 1 00000400 00000100 UNINITIALIZED

00000400 00000100 F28M35x_GlobalVariableDefs.obj (PieVectTableFile)

DmaRegsFile

* 1 00000500 000000e0 UNINITIALIZED

00000500 000000e0 F28M35x_GlobalVariableDefs.obj (DmaRegsFile)

ECap1RegsFile

* 1 000005e0 00000020 UNINITIALIZED

000005e0 00000020 F28M35x_GlobalVariableDefs.obj (ECap1RegsFile)

EPwm2RegsFile

* 1 00000600 00000080 UNINITIALIZED

00000600 00000080 F28M35x_GlobalVariableDefs.obj (EPwm2RegsFile)

EPwm3RegsFile

* 1 00000680 00000080 UNINITIALIZED

00000680 00000080 F28M35x_GlobalVariableDefs.obj (EPwm3RegsFile)

EPwm4RegsFile

* 1 00000700 00000080 UNINITIALIZED

00000700 00000080 F28M35x_GlobalVariableDefs.obj (EPwm4RegsFile)

EPwm5RegsFile

* 1 00000780 00000080 UNINITIALIZED

00000780 00000080 F28M35x_GlobalVariableDefs.obj (EPwm5RegsFile)

EPwm6RegsFile

* 1 00008100 00000080 UNINITIALIZED

00008100 00000080 F28M35x_GlobalVariableDefs.obj (EPwm6RegsFile)

EPwm7RegsFile

* 1 00008180 00000080 UNINITIALIZED

00008180 00000080 F28M35x_GlobalVariableDefs.obj (EPwm7RegsFile)

EPwm8RegsFile

* 1 00008200 00000080 UNINITIALIZED

00008200 00000080 F28M35x_GlobalVariableDefs.obj (EPwm8RegsFile)

EPwm9RegsFile

* 1 00008280 00000080 UNINITIALIZED

00008280 00000080 F28M35x_GlobalVariableDefs.obj (EPwm9RegsFile)

AnalogSysctrlRegsFile

* 1 00008300 00000078 UNINITIALIZED

00008300 00000078 F28M35x_GlobalVariableDefs.obj (AnalogSysctrlRegsFile)

CpuTimer0RegsFile

* 1 00008378 00000008 UNINITIALIZED

00008378 00000008 F28M35x_GlobalVariableDefs.obj (CpuTimer0RegsFile)

Adc2RegsFile

* 1 00008380 00000050 UNINITIALIZED

00008380 00000050 F28M35x_GlobalVariableDefs.obj (Adc2RegsFile)

McbspaRegsFile

* 1 000083d0 00000024 UNINITIALIZED

000083d0 00000024 F28M35x_GlobalVariableDefs.obj (McbspaRegsFile)

CpuTimer1RegsFile

* 1 000083f4 00000008 UNINITIALIZED

000083f4 00000008 F28M35x_GlobalVariableDefs.obj (CpuTimer1RegsFile)

EcslPwlFile

* 1 000083fc 00000004 UNINITIALIZED

000083fc 00000004 F28M35x_GlobalVariableDefs.obj (EcslPwlFile)

AdcRegsFile

* 1 00008400 00000050 UNINITIALIZED

00008400 00000050 F28M35x_GlobalVariableDefs.obj (AdcRegsFile)

EQep1RegsFile

* 1 00008450 00000022 UNINITIALIZED

00008450 00000022 F28M35x_GlobalVariableDefs.obj (EQep1RegsFile)

CpuTimer2RegsFile

* 1 00008472 00000008 UNINITIALIZED

00008472 00000008 F28M35x_GlobalVariableDefs.obj (CpuTimer2RegsFile)

NmiIntruptRegsFile

* 1 0000847a 00000006 UNINITIALIZED

0000847a 00000006 F28M35x_GlobalVariableDefs.obj (NmiIntruptRegsFile)

DevEmuRegsFile

* 1 00008480 00000042 UNINITIALIZED

00008480 00000042 F28M35x_GlobalVariableDefs.obj (DevEmuRegsFile)

RAMRegsFile

* 1 000084c2 0000003e UNINITIALIZED

000084c2 0000003e F28M35x_GlobalVariableDefs.obj (RAMRegsFile)

GpioCtrlRegsFile

* 1 00008500 00000040 UNINITIALIZED

00008500 00000040 F28M35x_GlobalVariableDefs.obj (GpioCtrlRegsFile)

GpioG1CtrlRegsFile

* 1 00008540 00000040 UNINITIALIZED

00008540 00000040 F28M35x_GlobalVariableDefs.obj (GpioG1CtrlRegsFile)

GpioG2CtrlRegsFile

* 1 00008580 0000003c UNINITIALIZED

00008580 0000003c F28M35x_GlobalVariableDefs.obj (GpioG2CtrlRegsFile)

FlashExeOnlyFile

* 1 000085bc 00000002 UNINITIALIZED

000085bc 00000002 F28M35x_GlobalVariableDefs.obj (FlashExeOnlyFile)

EQep2RegsFile

* 1 000085c0 00000022 UNINITIALIZED

000085c0 00000022 F28M35x_GlobalVariableDefs.obj (EQep2RegsFile)

SysCtrlRegsFile

* 1 000085e2 0000001d UNINITIALIZED

000085e2 0000001d F28M35x_GlobalVariableDefs.obj (SysCtrlRegsFile)

EQep3RegsFile

* 1 00008600 00000022 UNINITIALIZED

00008600 00000022 F28M35x_GlobalVariableDefs.obj (EQep3RegsFile)

PieCtrlRegsFile

* 1 00008622 0000001a UNINITIALIZED

00008622 0000001a F28M35x_GlobalVariableDefs.obj (PieCtrlRegsFile)

I2caRegsFile

* 1 00008640 00000022 UNINITIALIZED

00008640 00000022 F28M35x_GlobalVariableDefs.obj (I2caRegsFile)

CsmRegsFile

* 1 00008662 00000016 UNINITIALIZED

00008662 00000016 F28M35x_GlobalVariableDefs.obj (CsmRegsFile)

CsmPwlFile

* 1 00008678 00000008 UNINITIALIZED

00008678 00000008 F28M35x_GlobalVariableDefs.obj (CsmPwlFile)

ECap2RegsFile

* 1 00008680 00000020 UNINITIALIZED

00008680 00000020 F28M35x_GlobalVariableDefs.obj (ECap2RegsFile)

ECap3RegsFile

* 1 000086a0 00000020 UNINITIALIZED

000086a0 00000020 F28M35x_GlobalVariableDefs.obj (ECap3RegsFile)

ECap4RegsFile

* 1 000086c0 00000020 UNINITIALIZED

000086c0 00000020 F28M35x_GlobalVariableDefs.obj (ECap4RegsFile)

ECap5RegsFile

* 1 000086e0 00000020 UNINITIALIZED

000086e0 00000020 F28M35x_GlobalVariableDefs.obj (ECap5RegsFile)

ECap6RegsFile

* 1 00008700 00000020 UNINITIALIZED

00008700 00000020 F28M35x_GlobalVariableDefs.obj (ECap6RegsFile)

GpioDataRegsFile

* 1 00008720 00000020 UNINITIALIZED

00008720 00000020 F28M35x_GlobalVariableDefs.obj (GpioDataRegsFile)

GpioG1DataRegsFile

* 1 00008740 00000020 UNINITIALIZED

00008740 00000020 F28M35x_GlobalVariableDefs.obj (GpioG1DataRegsFile)

GpioG1TripRegsFile

* 1 00008760 00000020 UNINITIALIZED

00008760 00000020 F28M35x_GlobalVariableDefs.obj (GpioG1TripRegsFile)

GpioG2DataRegsFile

* 1 00008780 00000020 UNINITIALIZED

00008780 00000020 F28M35x_GlobalVariableDefs.obj (GpioG2DataRegsFile)

GpioTripRegsFile

* 1 000087a0 00000020 UNINITIALIZED

000087a0 00000020 F28M35x_GlobalVariableDefs.obj (GpioTripRegsFile)

Adc1ResultFile

* 1 000087c0 00000010 UNINITIALIZED

000087c0 00000010 F28M35x_GlobalVariableDefs.obj (Adc1ResultFile)

Adc2ResultFile

* 1 000087d0 00000010 UNINITIALIZED

000087d0 00000010 F28M35x_GlobalVariableDefs.obj (Adc2ResultFile)

AdcResultFile

* 1 000087e0 00000010 UNINITIALIZED

000087e0 00000010 F28M35x_GlobalVariableDefs.obj (AdcResultFile)

SciaRegsFile

* 1 000087f0 00000010 UNINITIALIZED

000087f0 00000010 F28M35x_GlobalVariableDefs.obj (SciaRegsFile)

SpiaRegsFile

* 1 00008800 00000010 UNINITIALIZED

00008800 00000010 F28M35x_GlobalVariableDefs.obj (SpiaRegsFile)

XIntruptRegsFile

* 1 00008810 00000010 UNINITIALIZED

00008810 00000010 F28M35x_GlobalVariableDefs.obj (XIntruptRegsFile)

M3PllRegsFile

* 1 00008820 00000008 UNINITIALIZED

00008820 00000008 F28M35x_GlobalVariableDefs.obj (M3PllRegsFile)

Comp1RegsFile

* 1 00008828 00000007 UNINITIALIZED

00008828 00000007 F28M35x_GlobalVariableDefs.obj (Comp1RegsFile)

Comp2RegsFile

* 1 0000882f 00000007 UNINITIALIZED

0000882f 00000007 F28M35x_GlobalVariableDefs.obj (Comp2RegsFile)

Comp3RegsFile

* 1 00008836 00000007 UNINITIALIZED

00008836 00000007 F28M35x_GlobalVariableDefs.obj (Comp3RegsFile)

Comp4RegsFile

* 1 00008840 00000007 UNINITIALIZED

00008840 00000007 F28M35x_GlobalVariableDefs.obj (Comp4RegsFile)

Comp5RegsFile

* 1 00008847 00000007 UNINITIALIZED

00008847 00000007 F28M35x_GlobalVariableDefs.obj (Comp5RegsFile)

Comp6RegsFile

* 1 0000884e 00000007 UNINITIALIZED

0000884e 00000007 F28M35x_GlobalVariableDefs.obj (Comp6RegsFile)

GLOBAL DATA SYMBOLS: SORTED BY DATA PAGE

address data page name

-------- ---------------- ----

00000000 0 (00000000) _Adc1Regs

00000050 1 (00000040) _FlashEccRegs

00000074 1 (00000040) _EpiRegs

00000080 2 (00000080) _FlashCtrlRegs

00000202 8 (00000200) _RAMErrRegs

00000240 9 (00000240) _PieVectTableCopy

00000340 d (00000340) _EPwm1Regs

000003c0 f (000003c0) _CtoMIpcRegs

00000400 10 (00000400) _PieVectTable

00000500 14 (00000500) _DmaRegs

000005e0 17 (000005c0) _ECap1Regs

00000600 18 (00000600) _EPwm2Regs

00000680 1a (00000680) _EPwm3Regs

00000700 1c (00000700) _EPwm4Regs

00000780 1e (00000780) _EPwm5Regs

00008000 200 (00008000) __stack

00008100 204 (00008100) _EPwm6Regs

00008180 206 (00008180) _EPwm7Regs

00008200 208 (00008200) _EPwm8Regs

00008280 20a (00008280) _EPwm9Regs

00008300 20c (00008300) _AnalogSysctrlRegs

00008378 20d (00008340) _CpuTimer0Regs

00008380 20e (00008380) _Adc2Regs

000083d0 20f (000083c0) _McbspaRegs

000083f4 20f (000083c0) _CpuTimer1Regs

000083fc 20f (000083c0) _EcslPwl

00008400 210 (00008400) _AdcRegs

00008450 211 (00008440) _EQep1Regs

00008472 211 (00008440) _CpuTimer2Regs

0000847a 211 (00008440) _NmiIntruptRegs

00008480 212 (00008480) _DevEmuRegs

000084c2 213 (000084c0) _RAMRegs

00008500 214 (00008500) _GpioCtrlRegs

00008540 215 (00008540) _GpioG1CtrlRegs

00008580 216 (00008580) _GpioG2CtrlRegs

000085bc 216 (00008580) _FlashExeOnly

000085c0 217 (000085c0) _EQep2Regs

000085e2 217 (000085c0) _SysCtrlRegs

00008600 218 (00008600) _EQep3Regs

00008622 218 (00008600) _PieCtrlRegs

00008640 219 (00008640) _I2caRegs

00008662 219 (00008640) _CsmRegs

00008678 219 (00008640) _CsmPwl

00008680 21a (00008680) _ECap2Regs

000086a0 21a (00008680) _ECap3Regs

000086c0 21b (000086c0) _ECap4Regs

000086e0 21b (000086c0) _ECap5Regs

00008700 21c (00008700) _ECap6Regs

00008720 21c (00008700) _GpioDataRegs

00008740 21d (00008740) _GpioG1DataRegs

00008760 21d (00008740) _GpioG1TripRegs

00008780 21e (00008780) _GpioG2DataRegs

000087a0 21e (00008780) _GpioTripRegs

000087c0 21f (000087c0) _Adc1Result

000087d0 21f (000087c0) _Adc2Result

000087e0 21f (000087c0) _AdcResult

000087f0 21f (000087c0) _SciaRegs

00008800 220 (00008800) _SpiaRegs

00008810 220 (00008800) _XIntruptRegs

00008820 220 (00008800) _M3PllRegs

00008828 220 (00008800) _Comp1Regs

0000882f 220 (00008800) _Comp2Regs

00008836 220 (00008800) _Comp3Regs

00008840 221 (00008840) _Comp4Regs

00008847 221 (00008840) _Comp5Regs

0000884e 221 (00008840) _Comp6Regs

0000d0d2 343 (0000d0c0) _Fapi_GlobalInit

0000d0de 343 (0000d0c0) ___TI_cleanup_ptr

0000d0e0 343 (0000d0c0) ___TI_dtors_ptr

0000d0e2 343 (0000d0c0) __lock

0000d0e4 343 (0000d0c0) __unlock

0000d100 344 (0000d100) _pbuffer

0000d102 344 (0000d100) _Buffer32

0000d104 344 (0000d100) _err

0000d140 345 (0000d140) _Buffer

0000e140 385 (0000e140) _PieVectTableInit

GLOBAL SYMBOLS: SORTED ALPHABETICALLY BY Name

page address name

---- ------- ----

0 0000c000 .text

0 0000d097 C$$EXIT

0 0000d0b0 LL$$AND

0 0000d0b8 LL$$OR

0 0000d0c0 LL$$XOR

0 0000c837 _ADCINT1_ISR

0 0000c83c _ADCINT2_ISR

0 0000c922 _ADCINT3_ISR

0 0000c927 _ADCINT4_ISR

0 0000c92c _ADCINT5_ISR

0 0000c931 _ADCINT6_ISR

0 0000c936 _ADCINT7_ISR

0 0000c93b _ADCINT8_ISR

1 00000000 _Adc1Regs

1 000087c0 _Adc1Result

1 00008380 _Adc2Regs

1 000087d0 _Adc2Result

1 00008400 _AdcRegs

1 000087e0 _AdcResult

1 00008300 _AnalogSysctrlRegs

0 0000d140 _Buffer

0 0000d102 _Buffer32

0 0000c95e _CFLFSM_ISR

0 0000c959 _CFLSINGERR_ISR

0 0000c968 _CRAMACCVIOL_ISR

0 0000c963 _CRAMSINGERR_ISR

0 0000caee _CSMSecurityStatus

1 00008828 _Comp1Regs

1 0000882f _Comp2Regs

1 00008836 _Comp3Regs

1 00008840 _Comp4Regs

1 00008847 _Comp5Regs

1 0000884e _Comp6Regs

1 00008378 _CpuTimer0Regs

1 000083f4 _CpuTimer1Regs

1 00008472 _CpuTimer2Regs

1 00008678 _CsmPwl

1 00008662 _CsmRegs

0 0000ca9b _CsmUnlock

1 000003c0 _CtoMIpcRegs

0 0000c7e2 _DATALOG_ISR

0 0000c8f0 _DINTCH1_ISR

0 0000c8f5 _DINTCH2_ISR

0 0000c8fa _DINTCH3_ISR

0 0000c8ff _DINTCH4_ISR

0 0000c904 _DINTCH5_ISR

0 0000c909 _DINTCH6_ISR

1 00008480 _DevEmuRegs

1 00000500 _DmaRegs

0 0000c8a5 _ECAP1_INT_ISR

0 0000c8aa _ECAP2_INT_ISR

0 0000c8af _ECAP3_INT_ISR

0 0000c8b4 _ECAP4_INT_ISR

0 0000c8b9 _ECAP5_INT_ISR

0 0000c8be _ECAP6_INT_ISR

0 0000cafa _ECSLSecurityStatus

1 000005e0 _ECap1Regs

1 00008680 _ECap2Regs

1 000086a0 _ECap3Regs

1 000086c0 _ECap4Regs

1 000086e0 _ECap5Regs

1 00008700 _ECap6Regs

0 0000c977 _EMPTY_ISR

0 0000c7ec _EMUINT_ISR

0 0000c87d _EPWM1_INT_ISR

0 0000c855 _EPWM1_TZINT_ISR

0 0000c882 _EPWM2_INT_ISR

0 0000c85a _EPWM2_TZINT_ISR

0 0000c887 _EPWM3_INT_ISR

0 0000c85f _EPWM3_TZINT_ISR

0 0000c88c _EPWM4_INT_ISR

0 0000c864 _EPWM4_TZINT_ISR

0 0000c891 _EPWM5_INT_ISR

0 0000c869 _EPWM5_TZINT_ISR

0 0000c896 _EPWM6_INT_ISR

0 0000c86e _EPWM6_TZINT_ISR

0 0000c89b _EPWM7_INT_ISR

0 0000c873 _EPWM7_TZINT_ISR

0 0000c8a0 _EPWM8_INT_ISR

0 0000c878 _EPWM8_TZINT_ISR

0 0000c8d7 _EPWM9_INT_ISR

0 0000c8c3 _EPWM9_TZINT_ISR

1 00000340 _EPwm1Regs

1 00000600 _EPwm2Regs

1 00000680 _EPwm3Regs

1 00000700 _EPwm4Regs

1 00000780 _EPwm5Regs

1 00008100 _EPwm6Regs

1 00008180 _EPwm7Regs

1 00008200 _EPwm8Regs

1 00008280 _EPwm9Regs

0 0000c8c8 _EQEP1_INT_ISR

0 0000c8cd _EQEP2_INT_ISR

0 0000c8d2 _EQEP3_INT_ISR

1 00008450 _EQep1Regs

1 000085c0 _EQep2Regs

1 00008600 _EQep3Regs

1 000083fc _EcslPwl

0 0000cabc _EcslUnlock

0 0000d00c _EnableInterrupts

0 0000ccc7 _EndSetup1FlashAPI

1 00000074 _EpiRegs

0 0000cc2b _EraseFlashSector

0 0000d0d2 _Fapi_GlobalInit

0 0000cd49 _Fapi_calculateEcc

0 0000cd02 _Fapi_calculateFletcherChecksum

0 0000cf64 _Fapi_checkFsmForReady

0 0000c006 _Fapi_connectFlashPumpToCpu

0 0000c090 _Fapi_disableBanksForOtpWrite

0 0000ce0c _Fapi_doBlankCheck

0 0000ce4d _Fapi_doBlankCheckByByte

0 0000c4fc _Fapi_doMarginRead

0 0000c59e _Fapi_doMarginReadByByte

0 0000d060 _Fapi_doVerify

0 0000d06f _Fapi_doVerifyByByte

0 0000c07b _Fapi_enableBanksForOtpWrite

0 0000c334 _Fapi_flushPipeline

0 0000cb48 _Fapi_getBankSectors

0 0000cb23 _Fapi_getDeviceInfo

0 0000c000 _Fapi_getFsmStatus

0 0000cb06 _Fapi_getLibraryInfo

0 0000cfb4 _Fapi_initializeAPI

0 0000ceff _Fapi_isAddressEcc

0 0000d035 _Fapi_issueAsyncCommand

0 0000d015 _Fapi_issueAsyncCommandWithAddress

0 0000c038 _Fapi_issueFsmSuspendCommand

0 0000c610 _Fapi_issueProgrammingCommand

0 0000c7c2 _Fapi_issueProgrammingCommandForEccAddresses

0 0000cf24 _Fapi_remapEccAddress

0 0000ce87 _Fapi_serviceWatchdogTimer

0 0000c310 _Fapi_setActiveFlashBank

0 0000cedc _Fapi_setupBankSectorEnable

0 0000ce89 _Fapi_setupEepromSectorEnable

0 0000cd66 _Fapi_waitDelay

0 0000c057 _Fapi_writeEwaitValue

1 00000080 _FlashCtrlRegs

1 00000050 _FlashEccRegs

1 000085bc _FlashExeOnly

0 0000ca28 _FlashGainPump

0 0000ca35 _FlashLeavePump

0 0000cadb _GetEXEstatus

1 00008500 _GpioCtrlRegs

1 00008720 _GpioDataRegs

1 00008540 _GpioG1CtrlRegs

1 00008740 _GpioG1DataRegs

1 00008760 _GpioG1TripRegs

1 00008580 _GpioG2CtrlRegs

1 00008780 _GpioG2DataRegs

1 000087a0 _GpioTripRegs

0 0000c90e _I2CINT1A_ISR

0 0000c913 _I2CINT2A_ISR

1 00008640 _I2caRegs

0 0000c7f6 _ILLEGAL_ISR

0 0000c7d8 _INT13_ISR

0 0000c7dd _INT14_ISR

0 0000c9da _InitFlash

0 0000ca40 _InitPeripheralClocks

0 0000cfe8 _InitPieCtrl

0 0000d040 _InitPieVectTable

0 0000c986 _InitSysCtrl

0 0000c972 _LUF_ISR

0 0000c96d _LVF_ISR

0 0000cad3 _LockDevice

1 00008820 _M3PllRegs

0 0000c8e6 _MRINTA_ISR

0 0000c940 _MTOCIPC_INT1_ISR

0 0000c945 _MTOCIPC_INT2_ISR

0 0000c94a _MTOCIPC_INT3_ISR

0 0000c94f _MTOCIPC_INT4_ISR

0 0000c8eb _MXINTA_ISR

1 000083d0 _McbspaRegs

0 0000c7f1 _NMI_ISR

1 0000847a _NmiIntruptRegs

0 0000c97c _PIE_RESERVED

1 00008622 _PieCtrlRegs

1 00000400 _PieVectTable

1 00000240 _PieVectTableCopy

0 0000e140 _PieVectTableInit

0 0000cc73 _ProgramFlash

1 00000202 _RAMErrRegs

1 000084c2 _RAMRegs

0 0000c7e7 _RTOSINT_ISR

0 0000c918 _SCIRXINTA_ISR

0 0000c91d _SCITXINTA_ISR

0 0000c8dc _SPIRXINTA_ISR

0 0000c8e1 _SPITXINTA_ISR

1 000087f0 _SciaRegs

0 0000cbfc _SetupF021FlashAPI

0 0000c9ff _SetupFlash

1 00008800 _SpiaRegs

1 000085e2 _SysCtrlRegs

0 0000c84b _TINT0_ISR

0 0000c828 _USER10_ISR

0 0000c82d _USER11_ISR

0 0000c832 _USER12_ISR

0 0000c7fb _USER1_ISR

0 0000c800 _USER2_ISR

0 0000c805 _USER3_ISR

0 0000c80a _USER4_ISR

0 0000c80f _USER5_ISR

0 0000c814 _USER6_ISR

0 0000c819 _USER7_ISR

0 0000c81e _USER8_ISR

0 0000c823 _USER9_ISR

0 0000c850 _WAKEINT_ISR

0 0000c841 _XINT1_ISR

0 0000c846 _XINT2_ISR

0 0000c954 _XINT3_ISR

1 00008810 _XIntruptRegs

0 0000cd31 __Fapi_calculateOtpChecksum

0 0000c3fe __Fapi_checkRegionForValue

0 0000c47d __Fapi_checkRegionForValueByByte

0 0000ccd6 __Fapi_divideUnsignedLong

0 0000c00b __Fapi_issueFsmCommand

0 0000c37f __Fapi_loopRegionForValue

0 0000c34a __Fapi_loopRegionForValueByByte

0 0000cd3c __Fapi_scaleCycleValues

0 0000c0a0 __Fapi_setupSectorsForWrite

1 00008100 __STACK_END

abs 00000100 __STACK_SIZE

0 0000d0de ___TI_cleanup_ptr

0 0000d0e0 ___TI_dtors_ptr

abs ffffffff ___binit__

abs ffffffff ___c_args__

0 0000e26a ___cinit__

0 0000ccd2 ___error__

0 0000d0d1 ___etext__

abs ffffffff ___pinit__

0 0000c000 ___text__

0 0000d07e __args_main

0 0000d0e2 __lock

0 0000d0d0 __nop

0 0000d0cc __register_lock

0 0000d0c8 __register_unlock

1 00008000 __stack

0 0000d0e4 __unlock

0 0000d097 _abort

0 0000cf70 _c_int00

0 0000d104 _err

0 0000d099 _exit

0 0000cd80 _main

0 0000d100 _pbuffer

0 0000c981 _rsvd_ISR

abs ffffffff binit

0 0000e26a cinit

0 0000e28a code_start

0 0000d0d1 etext

abs ffffffff pinit

GLOBAL SYMBOLS: SORTED BY Symbol Address

page address name

---- ------- ----

0 0000c000 .text

0 0000c000 _Fapi_getFsmStatus

0 0000c000 ___text__

0 0000c006 _Fapi_connectFlashPumpToCpu

0 0000c00b __Fapi_issueFsmCommand

0 0000c038 _Fapi_issueFsmSuspendCommand

0 0000c057 _Fapi_writeEwaitValue

0 0000c07b _Fapi_enableBanksForOtpWrite

0 0000c090 _Fapi_disableBanksForOtpWrite

0 0000c0a0 __Fapi_setupSectorsForWrite

0 0000c310 _Fapi_setActiveFlashBank

0 0000c334 _Fapi_flushPipeline

0 0000c34a __Fapi_loopRegionForValueByByte

0 0000c37f __Fapi_loopRegionForValue

0 0000c3fe __Fapi_checkRegionForValue

0 0000c47d __Fapi_checkRegionForValueByByte

0 0000c4fc _Fapi_doMarginRead

0 0000c59e _Fapi_doMarginReadByByte

0 0000c610 _Fapi_issueProgrammingCommand

0 0000c7c2 _Fapi_issueProgrammingCommandForEccAddresses

0 0000c7d8 _INT13_ISR

0 0000c7dd _INT14_ISR

0 0000c7e2 _DATALOG_ISR

0 0000c7e7 _RTOSINT_ISR

0 0000c7ec _EMUINT_ISR

0 0000c7f1 _NMI_ISR

0 0000c7f6 _ILLEGAL_ISR

0 0000c7fb _USER1_ISR

0 0000c800 _USER2_ISR

0 0000c805 _USER3_ISR

0 0000c80a _USER4_ISR

0 0000c80f _USER5_ISR

0 0000c814 _USER6_ISR

0 0000c819 _USER7_ISR

0 0000c81e _USER8_ISR

0 0000c823 _USER9_ISR

0 0000c828 _USER10_ISR

0 0000c82d _USER11_ISR

0 0000c832 _USER12_ISR

0 0000c837 _ADCINT1_ISR

0 0000c83c _ADCINT2_ISR

0 0000c841 _XINT1_ISR

0 0000c846 _XINT2_ISR

0 0000c84b _TINT0_ISR

0 0000c850 _WAKEINT_ISR

0 0000c855 _EPWM1_TZINT_ISR

0 0000c85a _EPWM2_TZINT_ISR

0 0000c85f _EPWM3_TZINT_ISR

0 0000c864 _EPWM4_TZINT_ISR

0 0000c869 _EPWM5_TZINT_ISR

0 0000c86e _EPWM6_TZINT_ISR

0 0000c873 _EPWM7_TZINT_ISR

0 0000c878 _EPWM8_TZINT_ISR

0 0000c87d _EPWM1_INT_ISR

0 0000c882 _EPWM2_INT_ISR

0 0000c887 _EPWM3_INT_ISR

0 0000c88c _EPWM4_INT_ISR

0 0000c891 _EPWM5_INT_ISR

0 0000c896 _EPWM6_INT_ISR

0 0000c89b _EPWM7_INT_ISR

0 0000c8a0 _EPWM8_INT_ISR

0 0000c8a5 _ECAP1_INT_ISR

0 0000c8aa _ECAP2_INT_ISR

0 0000c8af _ECAP3_INT_ISR

0 0000c8b4 _ECAP4_INT_ISR

0 0000c8b9 _ECAP5_INT_ISR

0 0000c8be _ECAP6_INT_ISR

0 0000c8c3 _EPWM9_TZINT_ISR

0 0000c8c8 _EQEP1_INT_ISR

0 0000c8cd _EQEP2_INT_ISR

0 0000c8d2 _EQEP3_INT_ISR

0 0000c8d7 _EPWM9_INT_ISR

0 0000c8dc _SPIRXINTA_ISR

0 0000c8e1 _SPITXINTA_ISR

0 0000c8e6 _MRINTA_ISR

0 0000c8eb _MXINTA_ISR

0 0000c8f0 _DINTCH1_ISR

0 0000c8f5 _DINTCH2_ISR

0 0000c8fa _DINTCH3_ISR

0 0000c8ff _DINTCH4_ISR

0 0000c904 _DINTCH5_ISR

0 0000c909 _DINTCH6_ISR

0 0000c90e _I2CINT1A_ISR

0 0000c913 _I2CINT2A_ISR

0 0000c918 _SCIRXINTA_ISR

0 0000c91d _SCITXINTA_ISR

0 0000c922 _ADCINT3_ISR

0 0000c927 _ADCINT4_ISR

0 0000c92c _ADCINT5_ISR

0 0000c931 _ADCINT6_ISR

0 0000c936 _ADCINT7_ISR

0 0000c93b _ADCINT8_ISR

0 0000c940 _MTOCIPC_INT1_ISR

0 0000c945 _MTOCIPC_INT2_ISR

0 0000c94a _MTOCIPC_INT3_ISR

0 0000c94f _MTOCIPC_INT4_ISR

0 0000c954 _XINT3_ISR

0 0000c959 _CFLSINGERR_ISR

0 0000c95e _CFLFSM_ISR

0 0000c963 _CRAMSINGERR_ISR

0 0000c968 _CRAMACCVIOL_ISR

0 0000c96d _LVF_ISR

0 0000c972 _LUF_ISR

0 0000c977 _EMPTY_ISR

0 0000c97c _PIE_RESERVED

0 0000c981 _rsvd_ISR

0 0000c986 _InitSysCtrl

0 0000c9da _InitFlash

0 0000c9ff _SetupFlash

0 0000ca28 _FlashGainPump

0 0000ca35 _FlashLeavePump

0 0000ca40 _InitPeripheralClocks

0 0000ca9b _CsmUnlock

0 0000cabc _EcslUnlock

0 0000cad3 _LockDevice

0 0000cadb _GetEXEstatus

0 0000caee _CSMSecurityStatus

0 0000cafa _ECSLSecurityStatus

0 0000cb06 _Fapi_getLibraryInfo

0 0000cb23 _Fapi_getDeviceInfo

0 0000cb48 _Fapi_getBankSectors

0 0000cbfc _SetupF021FlashAPI

0 0000cc2b _EraseFlashSector

0 0000cc73 _ProgramFlash

0 0000ccc7 _EndSetup1FlashAPI

0 0000ccd2 ___error__

0 0000ccd6 __Fapi_divideUnsignedLong

0 0000cd02 _Fapi_calculateFletcherChecksum

0 0000cd31 __Fapi_calculateOtpChecksum

0 0000cd3c __Fapi_scaleCycleValues

0 0000cd49 _Fapi_calculateEcc

0 0000cd66 _Fapi_waitDelay

0 0000cd80 _main

0 0000ce0c _Fapi_doBlankCheck

0 0000ce4d _Fapi_doBlankCheckByByte

0 0000ce87 _Fapi_serviceWatchdogTimer

0 0000ce89 _Fapi_setupEepromSectorEnable

0 0000cedc _Fapi_setupBankSectorEnable

0 0000ceff _Fapi_isAddressEcc

0 0000cf24 _Fapi_remapEccAddress

0 0000cf64 _Fapi_checkFsmForReady

0 0000cf70 _c_int00

0 0000cfb4 _Fapi_initializeAPI

0 0000cfe8 _InitPieCtrl

0 0000d00c _EnableInterrupts

0 0000d015 _Fapi_issueAsyncCommandWithAddress

0 0000d035 _Fapi_issueAsyncCommand

0 0000d040 _InitPieVectTable

0 0000d060 _Fapi_doVerify

0 0000d06f _Fapi_doVerifyByByte

0 0000d07e __args_main

0 0000d097 C$$EXIT

0 0000d097 _abort

0 0000d099 _exit

0 0000d0b0 LL$$AND

0 0000d0b8 LL$$OR

0 0000d0c0 LL$$XOR

0 0000d0c8 __register_unlock

0 0000d0cc __register_lock

0 0000d0d0 __nop

0 0000d0d1 ___etext__

0 0000d0d1 etext

0 0000d0d2 _Fapi_GlobalInit

0 0000d0de ___TI_cleanup_ptr

0 0000d0e0 ___TI_dtors_ptr

0 0000d0e2 __lock

0 0000d0e4 __unlock

0 0000d100 _pbuffer

0 0000d102 _Buffer32

0 0000d104 _err

0 0000d140 _Buffer

0 0000e140 _PieVectTableInit

0 0000e26a ___cinit__

0 0000e26a cinit

0 0000e28a code_start

1 00000000 _Adc1Regs

1 00000050 _FlashEccRegs

1 00000074 _EpiRegs

1 00000080 _FlashCtrlRegs

1 00000202 _RAMErrRegs

1 00000240 _PieVectTableCopy

1 00000340 _EPwm1Regs

1 000003c0 _CtoMIpcRegs

1 00000400 _PieVectTable

1 00000500 _DmaRegs

1 000005e0 _ECap1Regs

1 00000600 _EPwm2Regs

1 00000680 _EPwm3Regs

1 00000700 _EPwm4Regs

1 00000780 _EPwm5Regs

1 00008000 __stack

1 00008100 _EPwm6Regs

1 00008100 __STACK_END

1 00008180 _EPwm7Regs

1 00008200 _EPwm8Regs

1 00008280 _EPwm9Regs

1 00008300 _AnalogSysctrlRegs

1 00008378 _CpuTimer0Regs

1 00008380 _Adc2Regs

1 000083d0 _McbspaRegs

1 000083f4 _CpuTimer1Regs

1 000083fc _EcslPwl

1 00008400 _AdcRegs

1 00008450 _EQep1Regs

1 00008472 _CpuTimer2Regs

1 0000847a _NmiIntruptRegs

1 00008480 _DevEmuRegs

1 000084c2 _RAMRegs

1 00008500 _GpioCtrlRegs

1 00008540 _GpioG1CtrlRegs

1 00008580 _GpioG2CtrlRegs

1 000085bc _FlashExeOnly

1 000085c0 _EQep2Regs

1 000085e2 _SysCtrlRegs

1 00008600 _EQep3Regs

1 00008622 _PieCtrlRegs

1 00008640 _I2caRegs

1 00008662 _CsmRegs

1 00008678 _CsmPwl

1 00008680 _ECap2Regs

1 000086a0 _ECap3Regs

1 000086c0 _ECap4Regs

1 000086e0 _ECap5Regs

1 00008700 _ECap6Regs

1 00008720 _GpioDataRegs

1 00008740 _GpioG1DataRegs

1 00008760 _GpioG1TripRegs

1 00008780 _GpioG2DataRegs

1 000087a0 _GpioTripRegs

1 000087c0 _Adc1Result

1 000087d0 _Adc2Result

1 000087e0 _AdcResult

1 000087f0 _SciaRegs

1 00008800 _SpiaRegs

1 00008810 _XIntruptRegs

1 00008820 _M3PllRegs

1 00008828 _Comp1Regs

1 0000882f _Comp2Regs

1 00008836 _Comp3Regs

1 00008840 _Comp4Regs

1 00008847 _Comp5Regs

1 0000884e _Comp6Regs

abs 00000100 __STACK_SIZE

abs ffffffff ___binit__

abs ffffffff ___c_args__

abs ffffffff ___pinit__

abs ffffffff binit

abs ffffffff pinit

[248 symbols]