Hi,

Need help setting up the TMS320F2837x one of the four 16 bit ADCs to perform continuous conversions and trigger an interrupt once a window high/low comparator level has been exceeded.

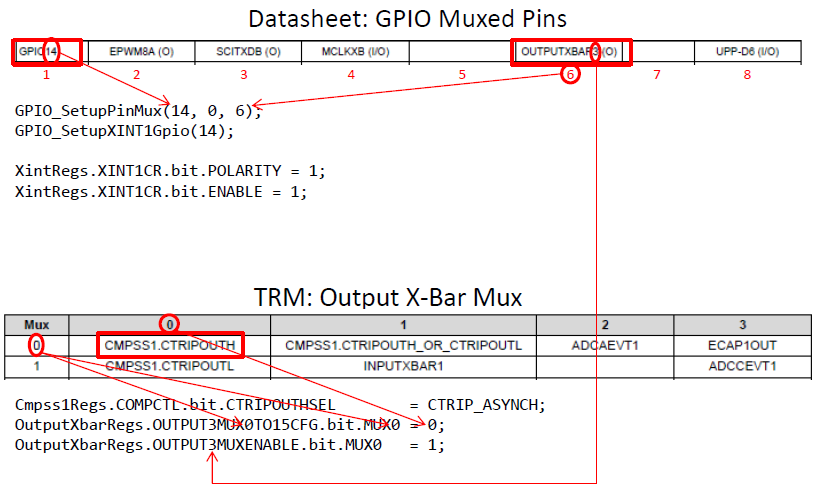

I guess my main Challenger since im new to the CPU is the PinMux. I played with the PinMux utility but it does not cover advance ADC stuff in much detail.

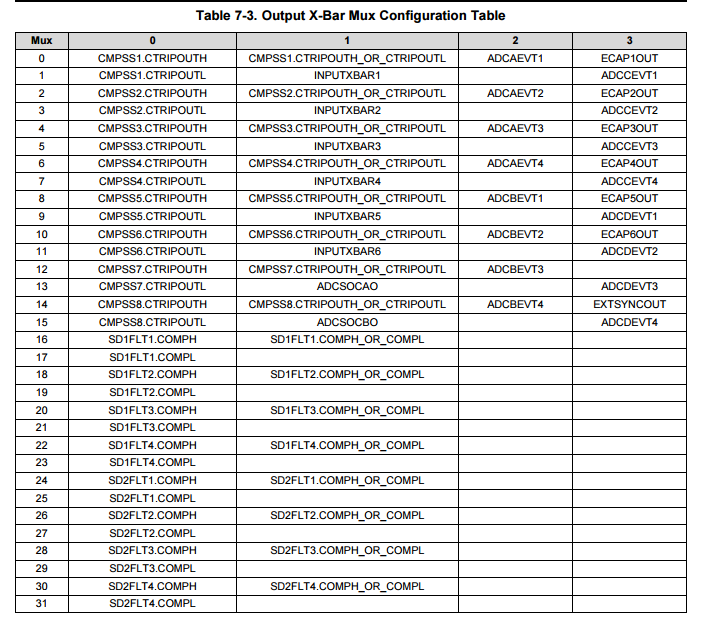

I am not quite sure how the INPUTXBAR and OUTPUTXBAR play into this. For now I just need to get the basic ADC running of which there seem to be plenty of examples.

However the tricky part is connecting the window comparator to the ADC channel, setting comparator setpoints and somehow get it to generate interrupts. The other challenge is how to trace the control flag registers to be able to know the source of the interrupt e.g. which adc channel and what level etc. And then there is the XBAR which I have not quite got my head wrapped arround +1000 pages of data sheets.

Anyhow I am trying to get as much out of this forum to speed up the learning curve - please bare with me.

I have the development system setup and running using the Launchpad. Can download and debug the examples.

Code snippeds and suggestions would be greatly welcomed just to get me started in the shortest amount of time

Thanks

Nick Amos