hi:

When I use F28020 ADC modul find some chennal cann't read ADC result .

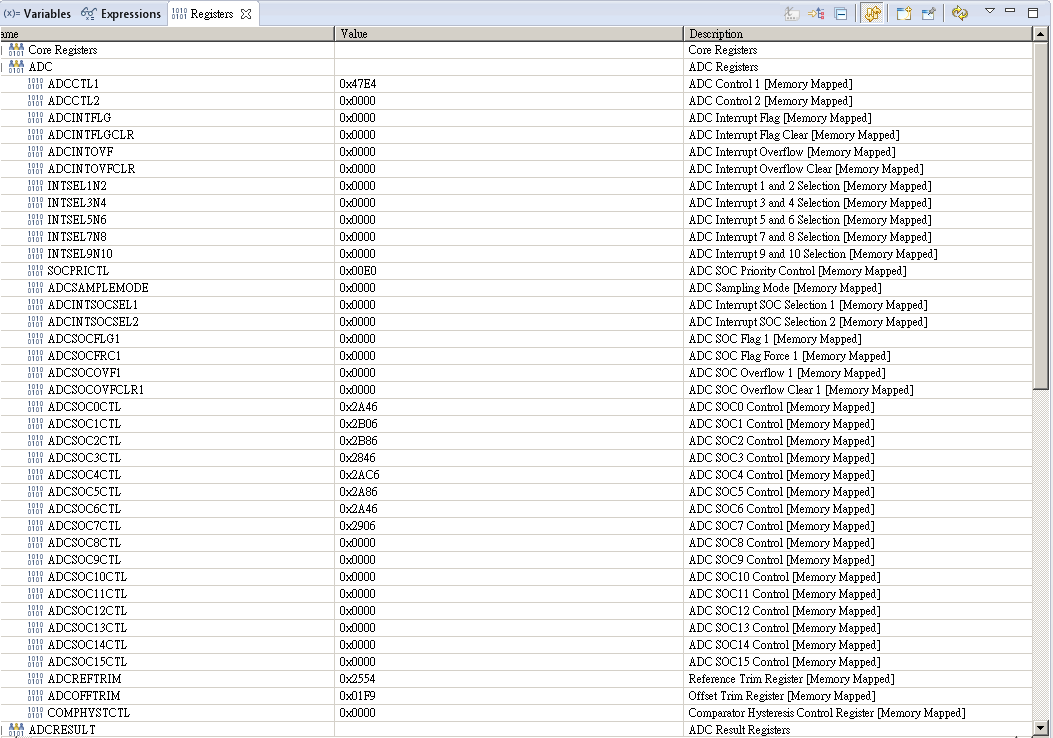

set ADC register as follow:

extern void DSP28x_usDelay(unsigned long Count);

#define ADC_MACRO_INIT() \

\

DELAY_US(ADC_usDELAY); \

AdcRegs.ADCCTL1.all=ADC_RESET_FLAG; \

asm(" NOP "); \

asm(" NOP "); \

\

EALLOW; \

AdcRegs.ADCCTL1.bit.ADCBGPWD = 1; /* Power up band gap */ \

\

DELAY_US(ADC_usDELAY); /* Delay before powering up rest of ADC */ \

\

AdcRegs.ADCCTL1.bit.ADCREFSEL = 0; \

AdcRegs.ADCCTL1.bit.ADCREFPWD = 1; /* Power up reference */ \

AdcRegs.ADCCTL1.bit.ADCPWDN = 1; /* Power up rest of ADC */ \

AdcRegs.ADCCTL1.bit.ADCENABLE = 1; /* Enable ADC */ \

\

asm(" RPT#100 || NOP"); \

\

AdcRegs.ADCCTL1.bit.INTPULSEPOS=1; \

AdcRegs.ADCCTL1.bit.TEMPCONV=0; \

\

DELAY_US(ADC_usDELAY); \

\

/******* CHANNEL SELECT *******/ \

\

AdcRegs.ADCSOC0CTL.bit.CHSEL = 0; /*Dummy meas. avoid 1st sample issue Rev0 Picollo*/ \

AdcRegs.ADCSOC0CTL.bit.TRIGSEL = 5; /*temperture sample*/ \

AdcRegs.ADCSOC0CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC1CTL.bit.CHSEL = 9; /* ChSelect: ADC B4-> Phase A Current */ \

AdcRegs.ADCSOC1CTL.bit.TRIGSEL = 5; /* Set SOC0 start trigger on EPWM1A */ \

AdcRegs.ADCSOC1CTL.bit.ACQPS = 6; /* Set SOC0 S/H Window to 6+1 ADC Clock Cycles */ \

\

AdcRegs.ADCSOC2CTL.bit.CHSEL = 1; /* ChSelect: ADC B6-> Phase B Current */ \

AdcRegs.ADCSOC2CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC2CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC3CTL.bit.CHSEL = 15; /* ChSelect: ADC A1-> DC Bus Voltage */ \

AdcRegs.ADCSOC3CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC3CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC4CTL.bit.CHSEL = 15; /* ChSelect: ADC B7-> V Phase A */ \

AdcRegs.ADCSOC4CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC4CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC5CTL.bit.CHSEL = 14; /* ChSelect: ADC B6-> V Phase B */ \

AdcRegs.ADCSOC5CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC5CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC6CTL.bit.CHSEL = 13; /* ChSelect: ADC B5-> V Phase C */ \

AdcRegs.ADCSOC6CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC6CTL.bit.ACQPS = 6; \

\

AdcRegs.ADCSOC7CTL.bit.CHSEL = 3; /* ChSelect: ADC A4-> Low Side DC Bus Return Cur.*/ \

AdcRegs.ADCSOC7CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC7CTL.bit.ACQPS = 6; \

\

\

AdcRegs.ADCSOC8CTL.bit.CHSEL = 11; /* expend speed input*/ \

AdcRegs.ADCSOC8CTL.bit.TRIGSEL = 5; \

AdcRegs.ADCSOC8CTL.bit.ACQPS = 8; \

EDIS; \

\

\

/* Set up Event Trigger with CNT_zero enable for Time-base of EPWM1 */ \

EPwm1Regs.ETSEL.bit.SOCAEN = 1; /* Enable SOCA */ \

EPwm1Regs.ETSEL.bit.SOCASEL = 1; /* Enable CNT_zero event for SOCA */ \

EPwm1Regs.ETPS.bit.SOCAPRD = 1; /* Generate SOCA on the 1st event */ \

EPwm1Regs.ETCLR.bit.SOCA = 1; /* Clear SOCA flag */

obver , I set ADSOC3 and ADSOC4 same channel , but in ADCRESULT , has not same result.

ADC cofigurate is below:

and this is epwm soca registor :

obver , we can see ETFLG is 0x0004 , that mean is socA is set . .

but whe I cann't get result3 ?

please check it ,please please !

best regard

fuyz