Hi !

I am using the TMS320F2837xS ADC , until now i have only used it with the 12bit single ended mode.

now i am going to work with a sensor that its output voltage will swing from 1 to 5 volts , while my ADC is referenced with 3V.

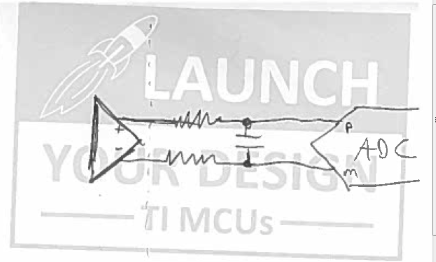

i am thinking of using the 16 bit differential mode so i can handle the high output voltage .

i have added my planed schematic and i will be very thankful if someone can give some feedback .

the ADC Vcm is 1.5v.

best regards

Mark