Hi,

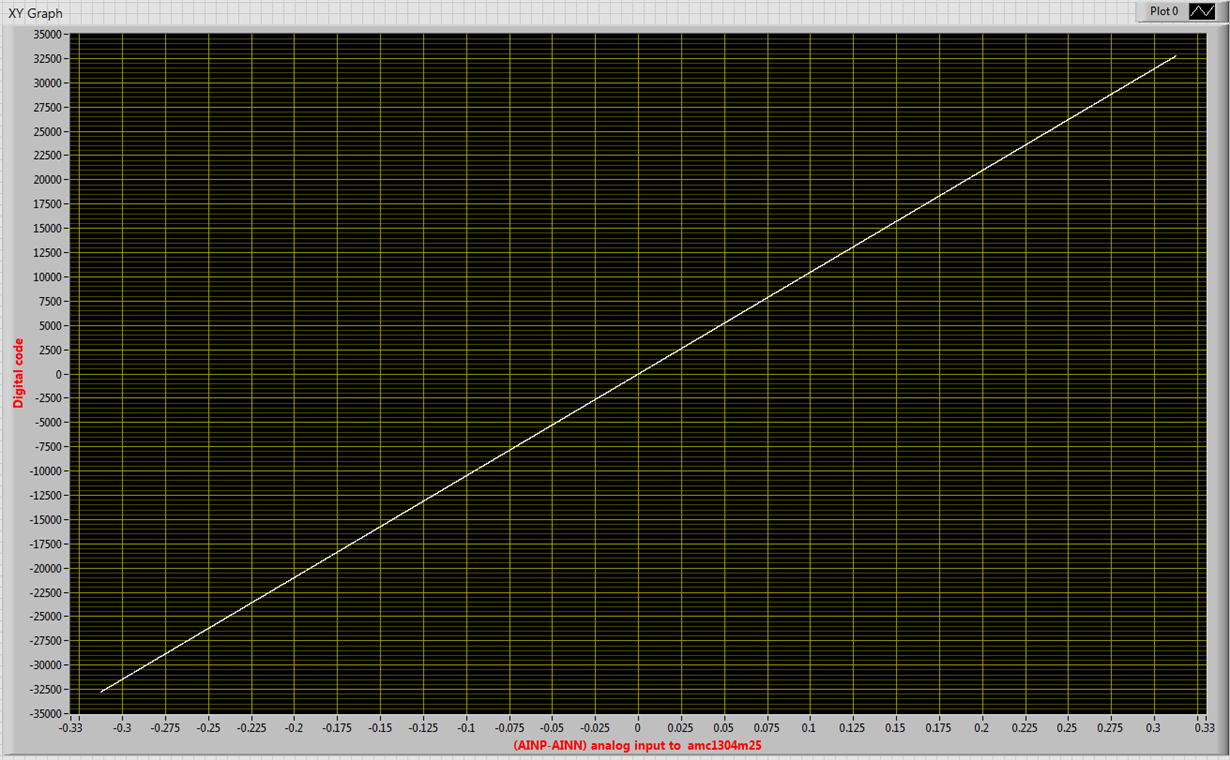

I am using AMC1304M25 Delta Sigma Modulator to implement shunt current measurements. The filter module is used from on chip SDFM peripheral from TMS320F28377S Launchpad. For this, I edited an example already available in ControlSuite for interrupt based SDFM: sdfm_filters_sync_cpu.

I want to use only one channel of SDFM1 at the moment where the signal acquisition source is function generator.

The edited code is given below: