I am trying to sample the analog signal through ADC of TMS320F28335. I have set the HSPCLK as 7.143MHz (100MHz/(2*7)), ADC CLK as 119.047 kHz (HSPCLK/60) and ACQ_PS as F(15). Therefore, the sampling rate is 7002 Hz ( 1/(2+ACQ_PS)*ADC CLK)). If 50HZ signal sampled. then it suppose to produce 140 sample per cycle. I tried to view the no. of samples using printf () function. but it leads memory space error. How can the no. of samples be confirmed ?

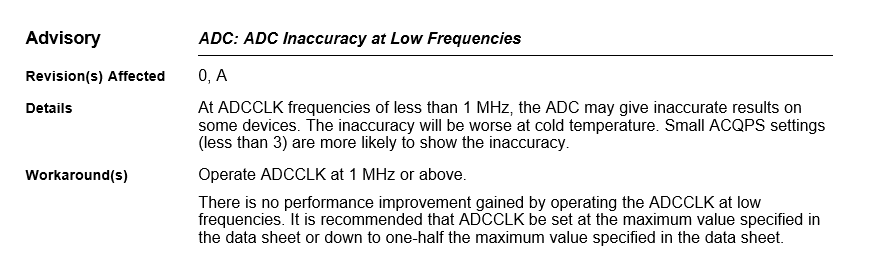

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.