Hello everybody ,

please we are designing a SW using M0 to pass paramaters after a Watchdog reset : we used in the past sma trick on F2806x and it was OK .

so basically after the Watchdog reset you run BootROM and then check these datain M0 to perform proper actions .

Now in F28377D I m on CPU1 and I see after a watchdog reset ( I wrote a wrong value in the Reg ) that M0 is inizialized at 0 and this is true for all memories ( INITDONE are "1" for all memory section )

now I checked in DS and it is not clear to me :

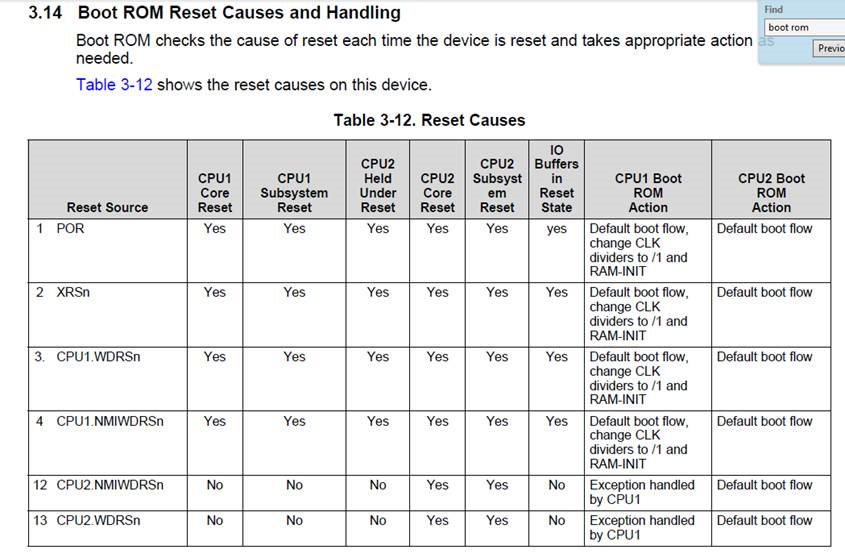

in table 3.12 it seems you can skip M0 & M1 inizialization as per the flow chart , in Table 3.14 it seems not feasible ( both tables attached ) .

please where am I wrong ?

what to check to be able NOT to inizialize M0 and M1 after a watchdog reset ?

thank you

bye

Carlo