Hello and merry Christmas,

During these days, I am trying to get familiar and understand the SCI (UART) interface between the F28335 DSP and my laptop using the ISR. Since I have never worked with UART, I am a little bit struggling. In particular, I attempt to read the data I send from my laptop to the DSP within the ISR. The minimum working example shall receive the data in the ISR and convert the ASCII information (variable named "ReceivedChar") into an integer (named "bla"). It also kind of works, but only kind of. What is happening:

1. When the code is running, I initially need to press a key 17 times (I press the key "1" on my keyboard, which shows me the equivalent of "49" in integer) until the ISR is called for the first time.

2. The code inside the ISR works fine, such that the ASCII "1" and the converterted ASCII into integer (49) give me the correct values. I leave the ISR again to come back to my main() function

3. I need to press a key 2 more times (I press key "2" on my keyboard which is equivalent to "50") until the ISR is called again. However, the value in "SciaRegs.SCIRXBUF.all" is not updated (SCIRXBUF.all has still the ASCII "1" information, i.e. "49").

4. I need to call the ISR 7 more times (i.e. 8 in total, i.e. pressing the key 16 times in total) until SCIRXBUF.all is updated to the new value. The new value is now 50 which matches with the ASCII table for the ASCII sign "2".

From now on, the whole procedure repeats to update the buffer to the new value, i.e. the ISR needs to be called 8 times until SCIRXBUF.all is updated to the new value.

I strongly believe that it is a software issue and I am messing up with variables, registers etc, as software development is not my strongest area. Any ideas on what is happening in my code?

Below the code, and thank for any help - much appreciated.

/*

* This example sets up the UART to send data to and receive data from the laptop

* When the data is received, an interrupt occurs and the data will then be taken from the buffer

*/

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

__interrupt void UART_isr(void);

void scia_init();

Uint16 bla;

Uint16 ReceivedChar;

void main(void) {

ReceivedChar=0;

bla=0;

// Step 1: Setting the PLL, Watchdog, enable peripheral clocks

InitSysCtrl();

// Step 3: Initialize the PIE control registers

// DINT; // Only necessary here if InitPieCtrl() does not have DINT; included

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

// Step 4: Initialize the PIE vector table to default ISR

InitPieVectTable();

// Configure the interrupt handling

// Setting up the XINT1 trigger, Table 112

EALLOW;

PieVectTable.SCIRXINTA = &UART_isr;

EDIS;

// Enable XINT1 in the PIE

// PieCtrlRegs.PIECTRL.bit.ENPIE = 1; // Enables the PIE interrupt table. Already done in InitPieVectTable();

PieCtrlRegs.PIEIER9.bit.INTx1 = 1; // Figure 87

IER |= M_INT9; // Sets the interrupt enable bit of group 9

EINT; // Enable global interrupts INTM

// Step 5: Initialize other device peripherals

// We need to initialize our SCI

InitSciGpio();

// Step 6: Write your code

scia_init(); // Initialize Sci FIFO

for(;;)

{

// Wait for inc character

while(SciaRegs.SCIFFRX.bit.RXFFST !=1) { } // wait for XRDY =1 for empty state

}

}

void scia_init()

{

/*

* FIFO configuration

*/

// SCIFFTX registers

SciaRegs.SCIFFTX.bit.SCIRST = 1; // Sci reset

SciaRegs.SCIFFTX.bit.SCIFFENA = 1; // Sci enhancements enabled

SciaRegs.SCIFFTX.bit.TXFIFOXRESET = 1; // Re-enable transmit FIFO operation

SciaRegs.SCIFFTX.bit.TXFFST = 0; // Transmit FIFO is empty

SciaRegs.SCIFFTX.bit.TXFFINTCLR = 1; // Clears TXFFINT flag

SciaRegs.SCIFFTX.bit.TXFFIENA = 0; // TX FIFO interrupt is disabled

// SCIFFRX registers

SciaRegs.SCIFFRX.bit.RXFIFORESET = 1; // Re-enable receive FIFO operation

SciaRegs.SCIFFRX.bit.RXFFINTCLR = 1; // Clears RXFFINT flag

SciaRegs.SCIFFRX.bit.RXFFIENA = 1; // RX FIFO interrupt is enabled

// SciaRegs.SCIFFRX.bit.RXFFIL = 0x1F; // 1111

// SCIFFCT registers

SciaRegs.SCIFFCT.all = 0; // Lets leave it as it is for now

/*

* Echoback configuration

*/

// SCICCR registers

SciaRegs.SCICCR.bit.STOPBITS = 0; // 1 stop bit

SciaRegs.SCICCR.bit.PARITY = 0; // Odd Parity - but will be disabled anyways

SciaRegs.SCICCR.bit.PARITYENA = 0; // Parity disabled

SciaRegs.SCICCR.bit.LOOPBKENA = 0; // Loopback test mode disabled

SciaRegs.SCICCR.bit.ADDRIDLE_MODE = 0; // Idle line mode

SciaRegs.SCICCR.bit.SCICHAR = 7; // 8 char bits

// SCICTL1 registers

SciaRegs.SCICTL1.bit.RXERRINTENA = 0; // Receive error interrupt disabled

SciaRegs.SCICTL1.bit.SWRESET = 0; // Initializing operating flags to the reset condition

SciaRegs.SCICTL1.bit.TXWAKE = 0; // Wake-up mode disabled

SciaRegs.SCICTL1.bit.SLEEP = 0; // Sleep mode disabled

SciaRegs.SCICTL1.bit.TXENA = 1; // Enable transmitter

SciaRegs.SCICTL1.bit.RXENA = 1; // Enable receiver

// SCICTL2 registers

SciaRegs.SCICTL2.bit.TXRDY = 0; // SCITXBUF is full

SciaRegs.SCICTL2.bit.TXEMPTY = 0; // Transmitter buffer is loaded with data

SciaRegs.SCICTL2.bit.RXBKINTENA = 1; // Receiver buffer interrupt enabled

SciaRegs.SCICTL2.bit.TXINTENA = 1; // TXRDY interrupt enabled

// SCIHBAUD registers for BAUD rate

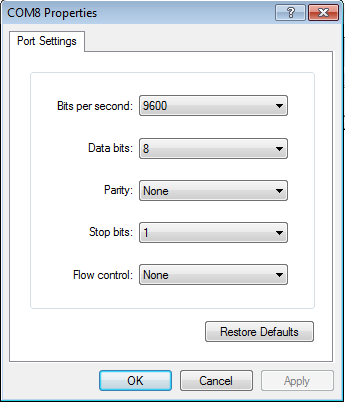

SciaRegs.SCIHBAUD =0x0001; // 9600 baud @LSPCLK = 37.5MHz.

SciaRegs.SCILBAUD =0x00E7;

// SCICTL1 registers again

SciaRegs.SCICTL1.all = 0x0023; // WTF?

}

__interrupt void UART_isr(void)

{

// Get character

ReceivedChar = SciaRegs.SCIRXBUF.all;

bla = ReceivedChar-'0';

SciaRegs.SCIFFRX.bit.RXFFOVRCLR=1; // Clear Overflow flag

SciaRegs.SCIFFRX.bit.RXFFINTCLR = 1; // Clears RXFFINT flag to enable new incoming interrupts

// Acknowledge this interrupt to get more from group 1

PieCtrlRegs.PIEACK.all = PIEACK_GROUP9;

}